Dsp6678

Когда говорят DSP6678, многие сразу думают о чистой вычислительной мощи, о терафлопсах. Но на практике, особенно при отладке на реальной плате, понимаешь, что главная история часто не в самом процессоре, а во всём, что его окружает. Вспоминается один проект, где мы использовали плату от ООО Сиань Циюнь Чжисюнь Электронные Технологии — они как раз предлагают комплексные решения, и это был не просто голый эвалюэйшн-кит. И вот тут начинается самое интересное, а порой и мучительное.

Первое впечатление и подводные камни

Плата пришла, вроде бы всё по спецификации. Загрузка через SYS/BIOS вроде пошла. Но сразу столкнулся с тем, что документация на периферию, особенно на нестандартные интерфейсы, которые добавил производитель, была... скажем так, сжатой. У DSP6678 своя сложная архитектура CorePac, и нужно было грамотно распределить задачи между ядрами. Первая ошибка — попытка грузить один и тот же образ на все ядра без тонкой настройки связей между ними через IPC. Получилась каша.

Помню, долго ломал голову над странными артефактами в данных при работе с EMIF. Оказалось, проблема была в настройках контроллера памяти на самой плате, которые были не до конца синхронизированы с рекомендациями TI для DSP6678. Пришлось лезть в исходники загрузчика и править инициализацию. Это тот момент, когда понимаешь ценность поставщика, который глубоко погружён в железо. Компания ООО Сиань Циюнь Чжисюнь Электронные Технологии, судя по их портфелю, как раз из таких — они не просто паяют компоненты, а занимаются интеграцией на уровне цепочки.

Была ещё забавная история с тактированием. На плате стоял свой генератор, и его стабильность была критична для высокоскоростных сериалов. Пришлось самостоятельно проверять джиттер осциллографом, потому что в описании платы была лишь номинальная частота. Вот эти мелкие, но затратные по времени нюансы и отличают работу с 'коробочным' решением от кастомной разработки.

Оптимизация под многозадачность: проб и ошибок было много

Когда перешли к реализации алгоритмов, стало ясно, что компилятор TI — инструмент мощный, но своенравный. Просто включить оптимизацию -O3 и ждать чуда — путь в никуда. Особенно для кода, работающего с разделяемой памятью. Пришлось вручную выравнивать структуры данных, активно использовать директивы pragma MUST_ITERATE и RESTRICT, чтобы дать компилятору понять наши намерения. Без этого DSP6678 не раскрывал и половины потенциала.

Один из болезненных уроков — работа с кэшем. Изначальная конфигурация L1/L2 для части ядер была неоптимальна, возникали частые промахи, которые 'съедали' всю пользу от параллельных вычислений. Пришлось потратить неделю на профилирование с помощью инструментов вроде TI Code Composer Studio и на переписывание критичных участков кода с учётом локальности данных. Это была рутина, но после этого производительность выросла кратно.

И ещё о памяти DDR. Её латентность — это отдельная песня. Мы пытались минимизировать обращения, но в одном из алгоритмов без этого было не обойтись. Решением стало предварительное формирование данных в более крупные блоки в памяти L2 с последующей асинхронной передачей на обработку. Сложно, зато сработало. Думаю, именно для таких сценариев интеграторы вроде Сиань Циюнь Чжисюнь Электронные Технологии и важны — они могут предложить платформу, где подобные моменты уже частично учтены на аппаратном уровне.

Вопросы отладки и взаимодействия с 'железом'

Отладка многопоточного кода на восьми ядрах — это особый вид искусства. JTAG-эмулятор XDS560v2 спасал, но иногда соединение 'отваливалось' при одновременной остановке нескольких ядер. Пришлось вырабатывать дисциплину: отлаживать поочерёдно, максимально изолируя функционал. Хорошо, что в DSP6678 есть мощные средства трассировки (ETB, STM), но их настройка — тоже не для слабонервных.

Реальный геморрой начался при интеграции с внешним FPGA, который стоял на той же плате. Очередь сообщений через RapidIO вроде работала, но под нагрузкой возникали потери пакетов. Долго искали причину: то ли в софте, то ли в разводке платы. В итоге оказалось, что нужно было вручную корректировать приоритеты виртуальных каналов в настройках RapidIO. Мелкая деталь в даташите, которую легко пропустить.

Это к вопросу о готовых решениях. Когда берёшь плату у компании, которая контролирует несколько предприятий по цепочке, как ООО Сиань Циюнь Чжисюнь Электронные Технологии, есть шанс, что такие межкомпонентные взаимодействия уже оттестированы. Но проверить всё равно придётся самому — слепому доверию не место.

Размышления о выборе платформы и экосистеме

Сейчас оглядываюсь назад и думаю: а был ли выбор DSP6678 абсолютно верным? Для задач цифровой обработки сигналов в реальном времени с жёсткими требованиями по детерминизму — безусловно, да. Его архитектура C66x с векторными расширениями идеальна для этого. Но для более гетерогенных задач, где нужна ещё и сложная логика управления, возможно, лучше смотрелась бы связка DSP + микроконтроллер или тот же FPGA.

Важный момент — поддержка. Сообщество вокруг процессоров TI обширное, но ответы на специфичные вопросы, особенно по низкоуровневому железу конкретной платы, приходилось искать долго. Здесь опять выходит на первый план роль интегратора. Если производитель платы, как заявлено в описании этой компании, создаёт синергетическую экосистему, то теоретически он должен предоставлять и более глубокую поддержку, включая примеры кода и патчи для драйверов.

В нашем случае часть драйверов для периферии на плате пришлось допиливать самостоятельно. Это дало бесценный опыт, но отняло время. Для коммерческого проекта с жёсткими сроками такой подход рискован. Поэтому сейчас, выбирая платформу, я всегда смотрю не только на характеристики чипа, но и на зрелость и открытость программной экосистемы от поставщика платы.

Итоги и взгляд вперёд

Работа с DSP6678 — это всегда вызов. Это не микроконтроллер, который можно быстро 'завести'. Это мощный инструмент, требующий глубокого понимания как его внутренней архитектуры, так и системы в целом. Основные сложности, с которыми мы столкнулись, лежали не в плоскости математики алгоритмов, а в низкоуровневой настройке, синхронизации ядер и работе с памятью.

Опыт взаимодействия с платой от интегратора показал, насколько важно, чтобы поставщик понимал все тонкости своего продукта. Когда компания, как ООО Сиань Циюнь Чжисюнь Электронные Технологии, позиционирует себя как часть промышленной цепочки, это вызывает доверие. Но доверие нужно подтверждать качеством документации и отзывчивой технической поддержкой.

Сейчас появляются новые процессоры, но принципы остаются. Любая мощная платформа — это компромисс между производительностью, сложностью разработки и надёжностью конечного решения. DSP6678 научил меня смотреть на проект целиком: от схемы питания на плате до стратегии распределения данных между ядрами. И этот урок, пожалуй, дороже любого терафлопса.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

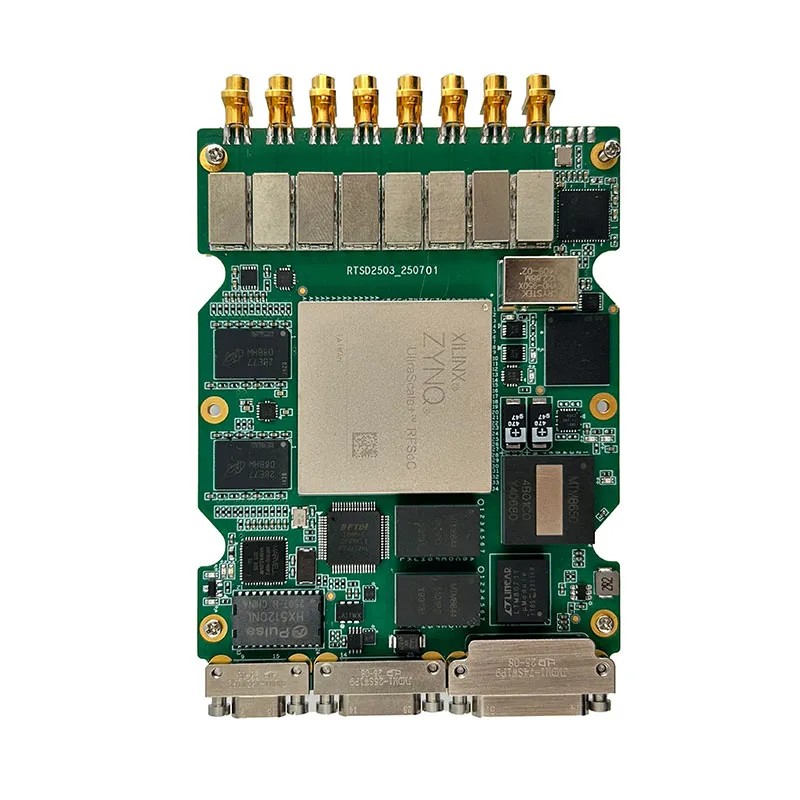

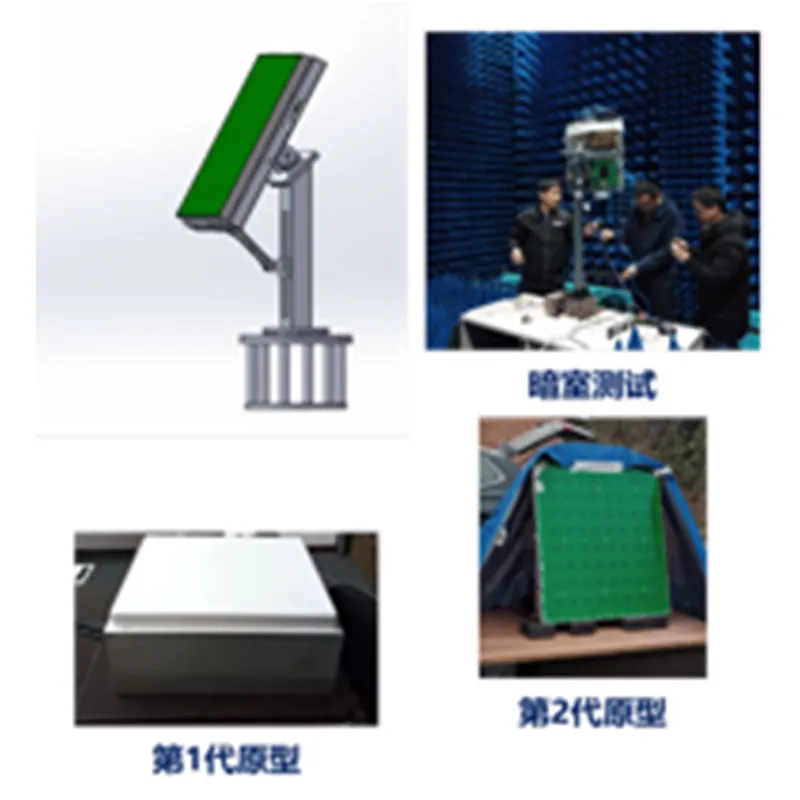

8T8R прототип программируемой РЛС

8T8R прототип программируемой РЛС -

Обработка и отслеживание изображений

Обработка и отслеживание изображений -

Разработка программного обеспечения

Разработка программного обеспечения -

Агентская продажа электронных компонентов

Агентская продажа электронных компонентов -

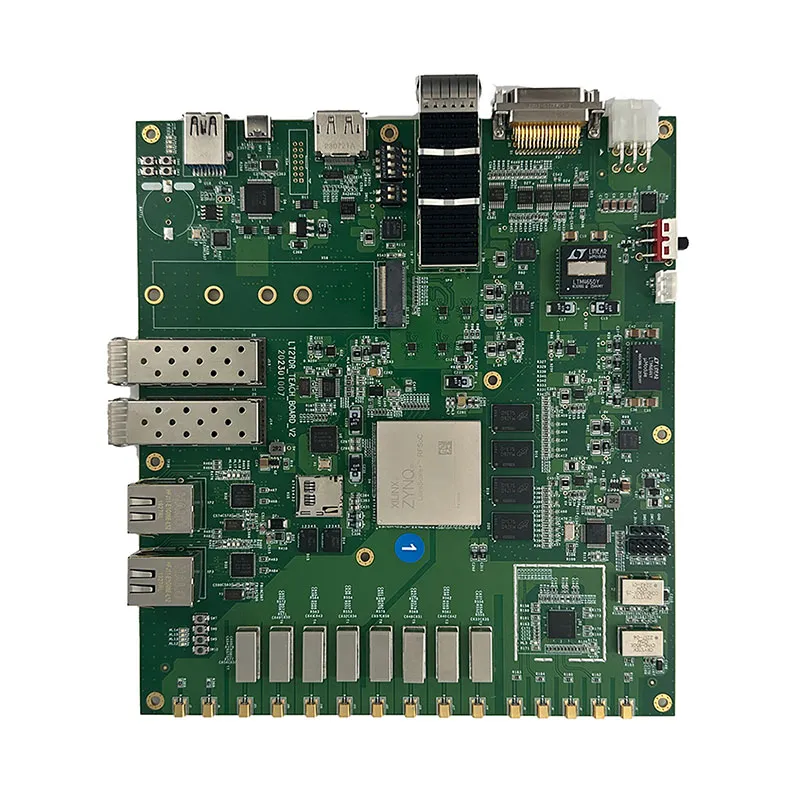

Высокоскоростной сбор и хранение данных: Прямая запись FPGA в NVMe SSD (двухдисковый отсек)

Высокоскоростной сбор и хранение данных: Прямая запись FPGA в NVMe SSD (двухдисковый отсек) -

TC49DR-8T9R

TC49DR-8T9R -

16T16R полностью цифровая РЛС Ka-диапазона

16T16R полностью цифровая РЛС Ka-диапазона -

4T32R голографическая статическая РЛС

4T32R голографическая статическая РЛС -

Обучение разработке на ПЛИС (FPGA)

Обучение разработке на ПЛИС (FPGA) -

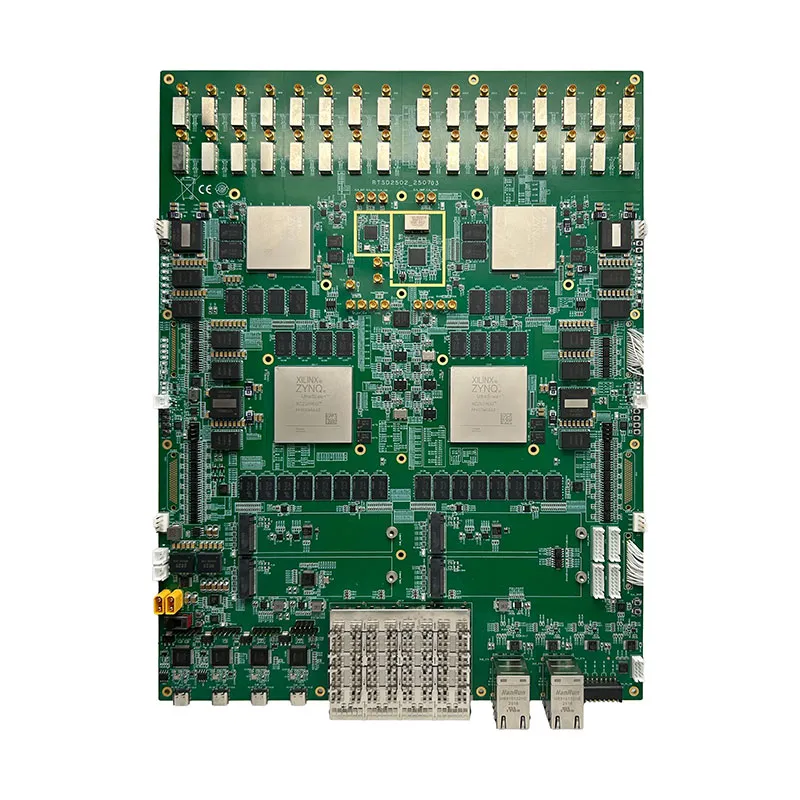

RTSD2502_250703

RTSD2502_250703 -

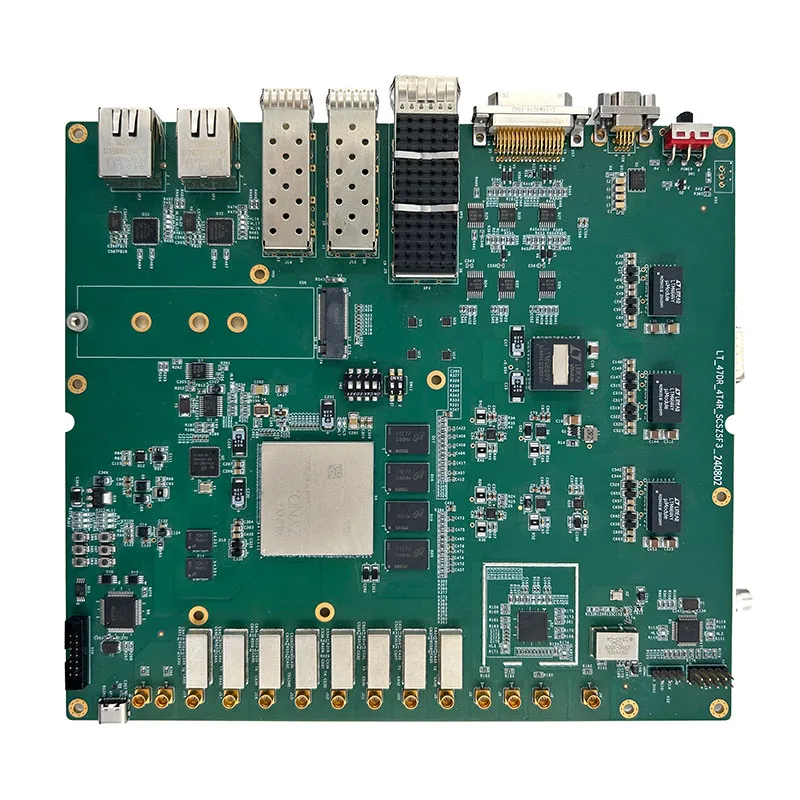

Плата высокоскоростной маршрутизации и коммутации данных VU13P

Плата высокоскоростной маршрутизации и коммутации данных VU13P -

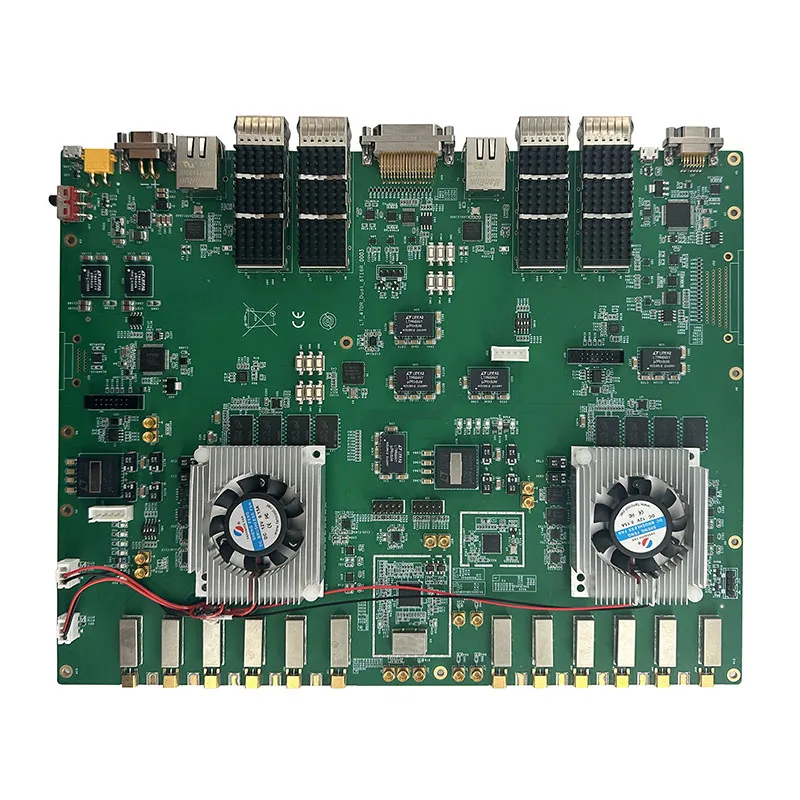

47DR_DUAL_6T16

47DR_DUAL_6T16