Продукция

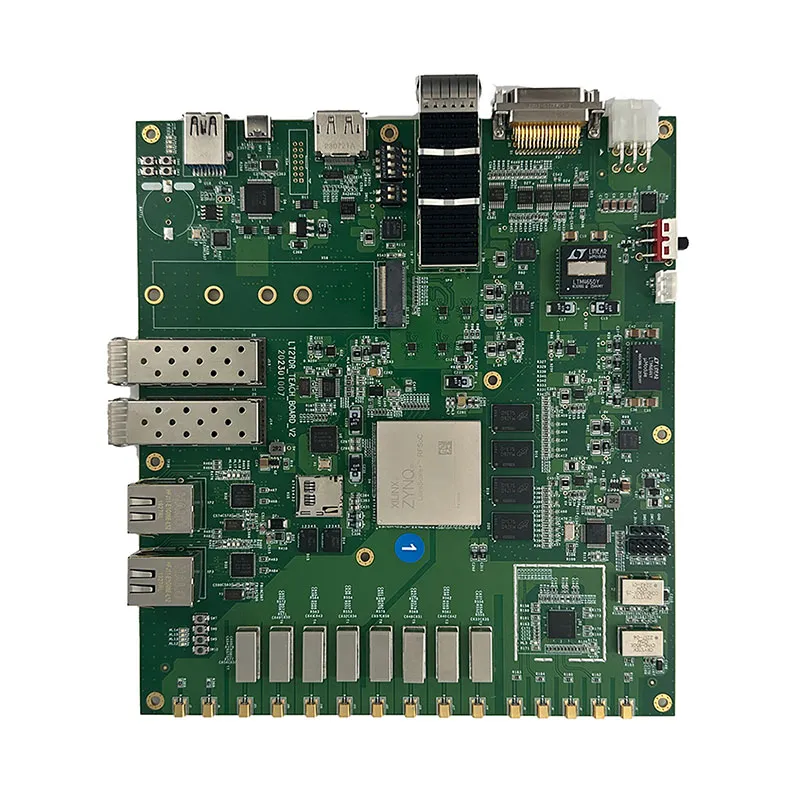

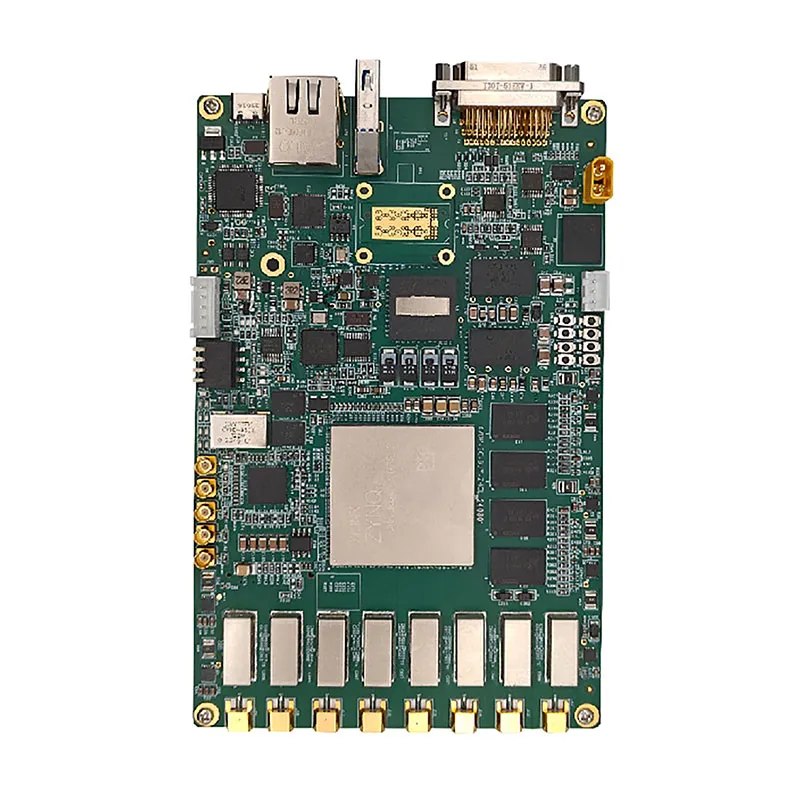

49DR_SV3

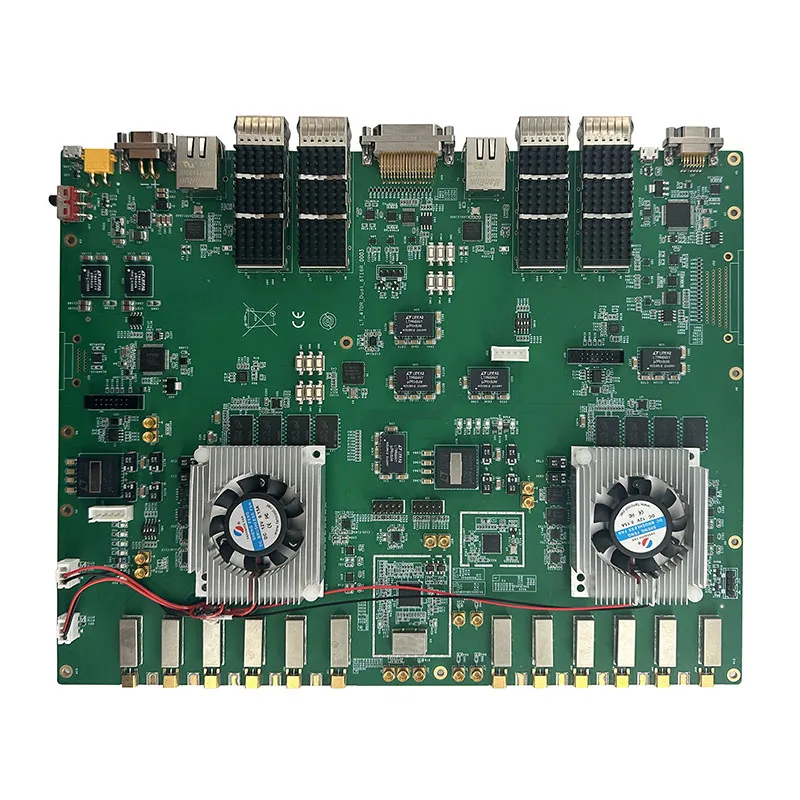

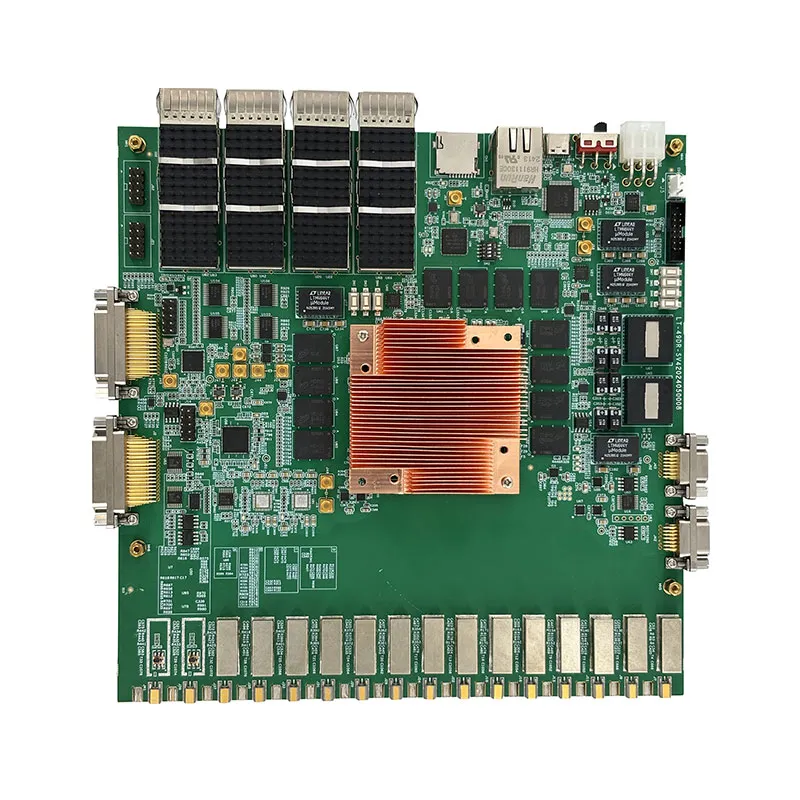

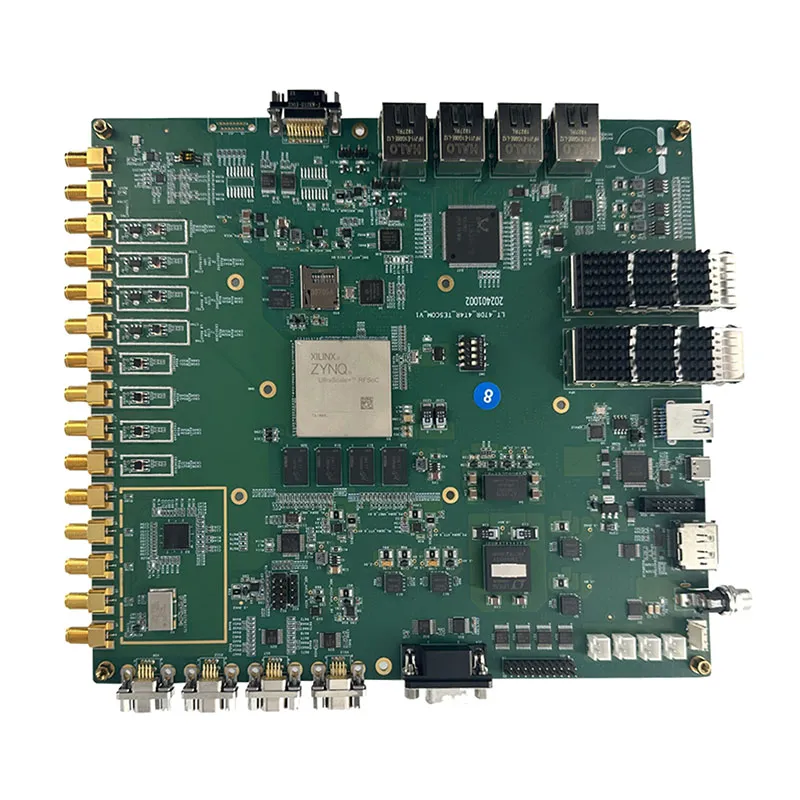

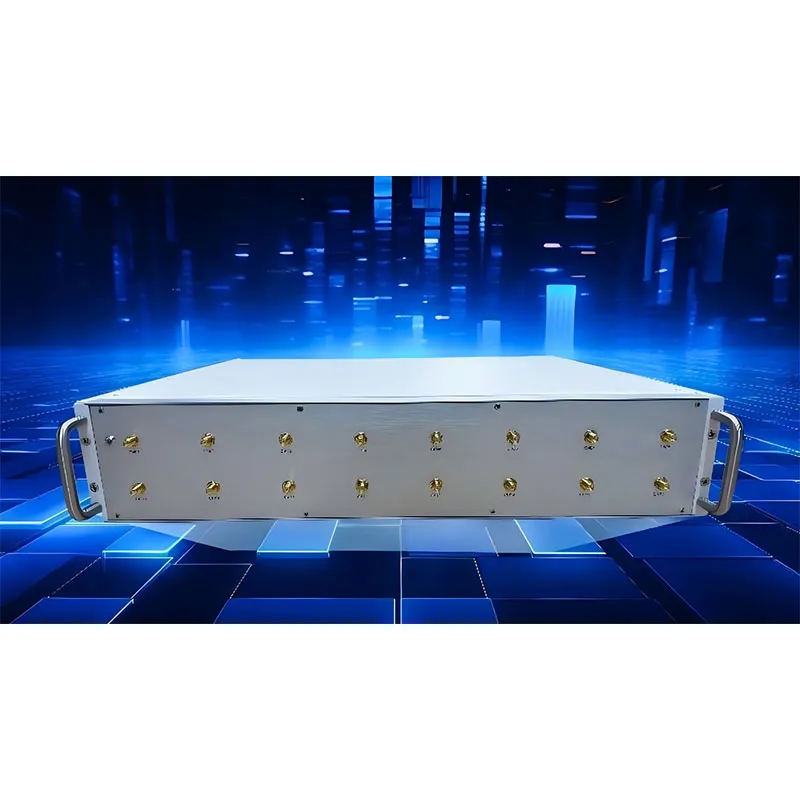

Описание продукта Плата цифрового массива 49DR_SV3 использует XCZU49DR в качестве основной микросхемы управления, оптимизирует тактовые характеристики, а также фазовый шум, внутриимпульсное отношение сигнал/шум, SFDR и индекс межканальной изоляции для применения в радарах. Плата имеет богатые ...

Описание

маркер

Описание продукта

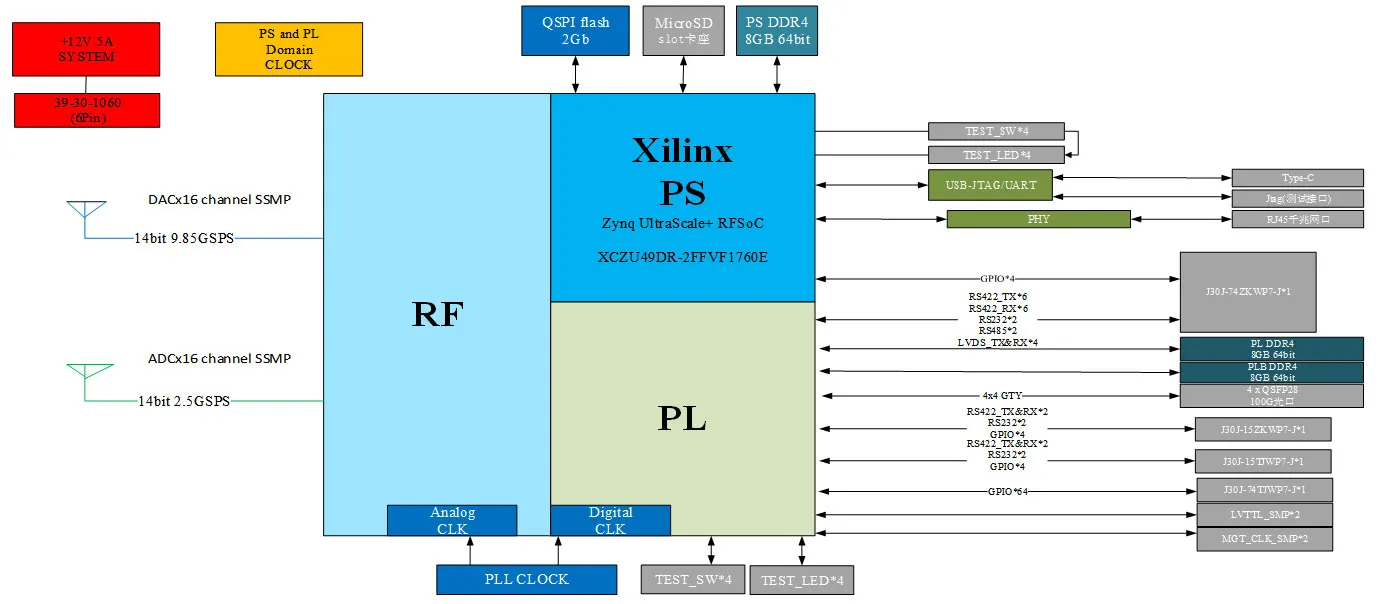

Плата цифрового массива 49DR_SV3 использует XCZU49DR в качестве основной микросхемы управления, оптимизирует тактовые характеристики, а также фазовый шум, внутриимпульсное отношение сигнал/шум, SFDR и индекс межканальной изоляции для применения в радарах. Плата имеет богатые периферийные интерфейсы, отличную межканальную согласованность и поддерживает каскадирование нескольких плат, что имеет выдающиеся преимущества в приложениях для радаров с цифровыми массивами.

Особенности продукта

Поддержка 16 передатчиков и 16 приемников

Поддержка прямого приема радиочастот DC-6 ГГц

Поддержка высокоскоростной передачи данных, 4-сторонний оптический порт 100G

Поддержка межплатного каскадирования

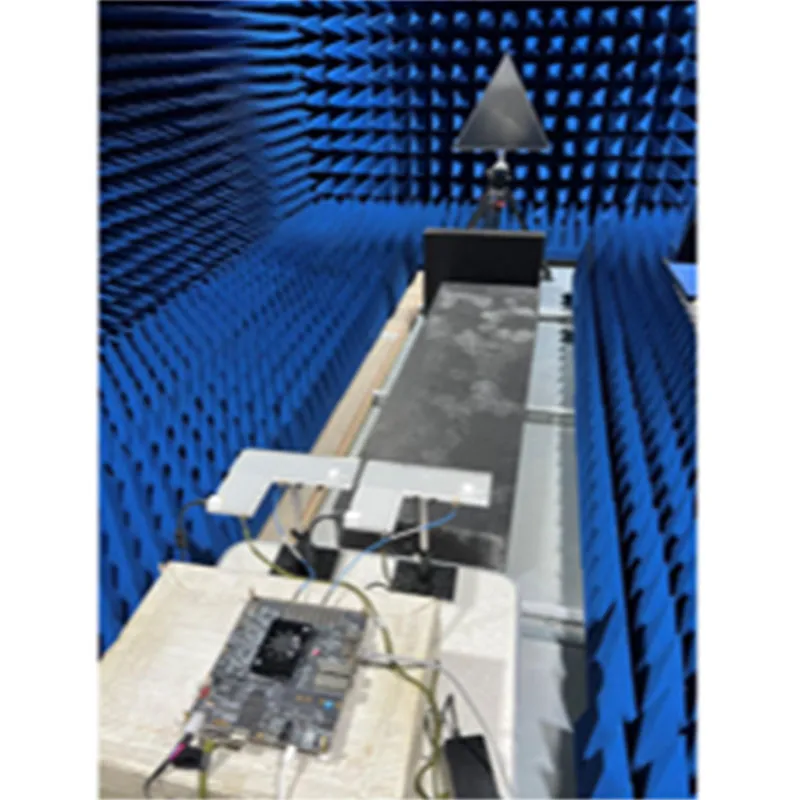

Направление применения

Радар с цифровой решеткой, радар MIMO

Цифровые радары, радары MIMO; крупномасштабная связь MIMO; обнаружение и прием массивов; квантовые вычисления.

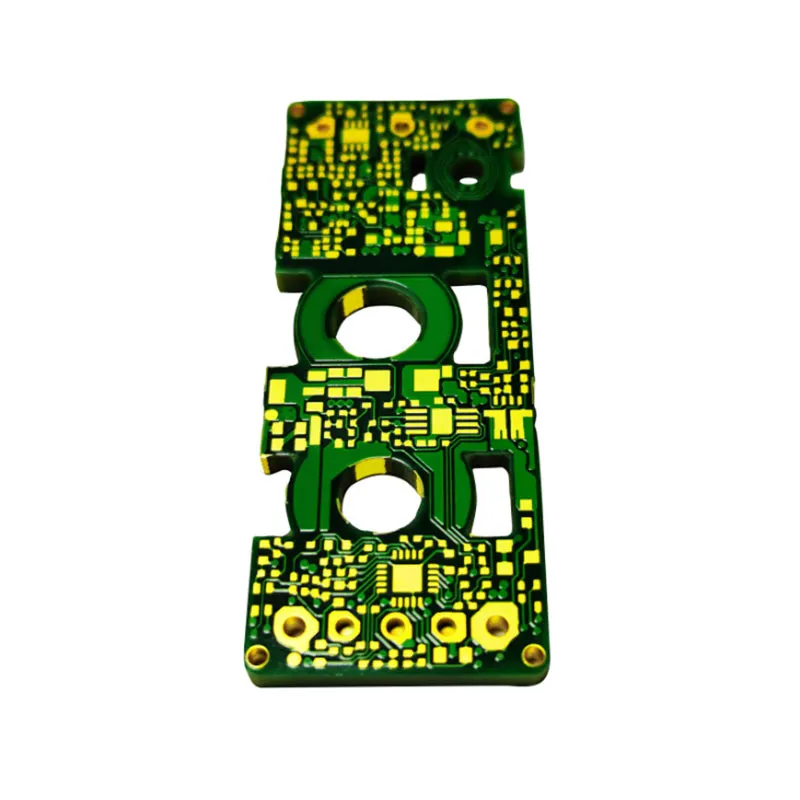

Вспомогательные аксессуары

Программное обеспечение для управления верхним компьютером MATLAB; проект однотонального тестирования, проект шлейфового тестирования, проект синхронного тестирования.

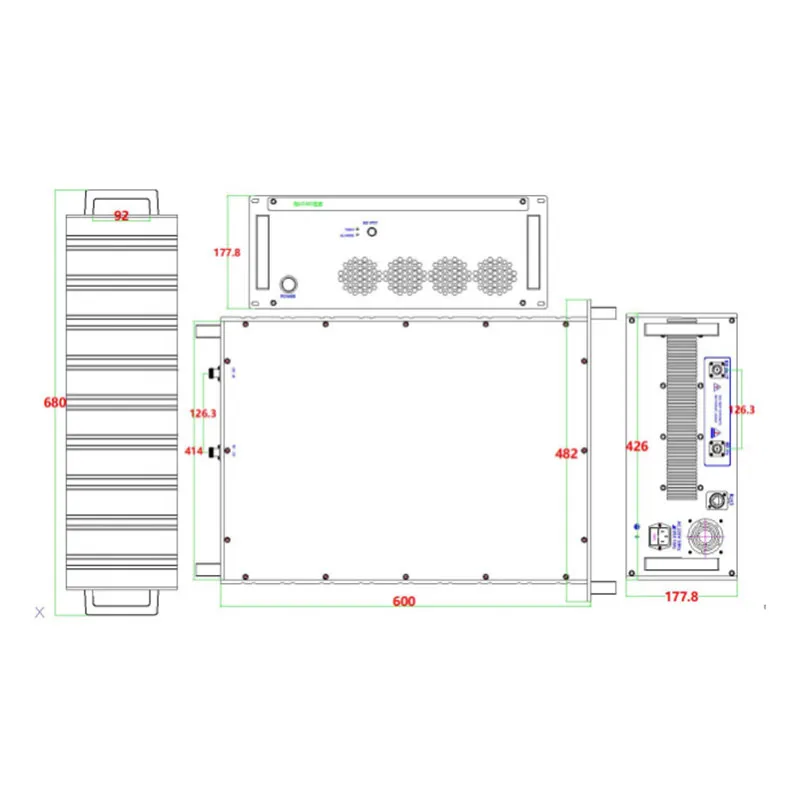

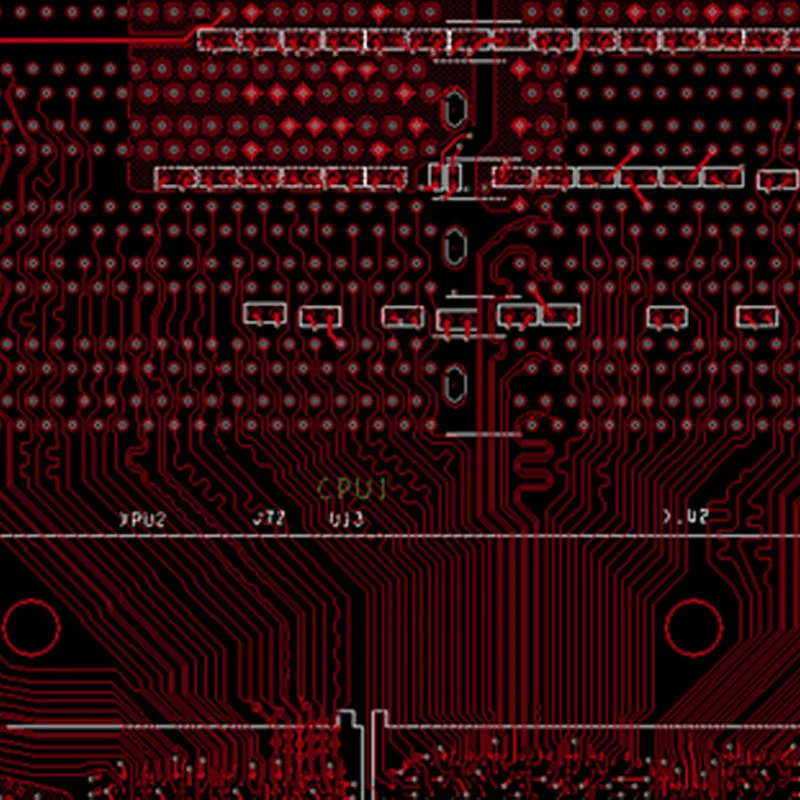

Архитектура продукта

Параметр продукта

| Номер модели: 49DR_SV3 | Количество каналов: 16 передатчиков и 16 приемников |

| Модель основного чипа: XCZU49DR-2FFVF1760E | Частота радиочастот: DC-6 ГГц |

| Семейство микросхем: Zynq UltraScale+RFSoC | Частота дискретизации АЦП: 2.5GSPS |

| ARM: четырехъядерный Cortex-A53, двухъядерный Cortex-R5 | Частота дискретизации ЦАП: 9,85GSPS |

| System Logic Cells(K):930 | Изоляция между каналами: >60 дБ |

| DSP Slices:4,272 | Разрядность АЦП: 14 бит |

| Total Block RAM(Mb):38 | Количество бит ЦАП: 14 бит |

| PCle:Gen3x16/Gen4×8/CCIX×2 | Выходная мощность ЦАП: -10dBm@typ |

| GTY:16 | SFDR:65dBc@typ |

| QSPI Flash:2Gb | Размер :225мм×205мм |

| Поддержка :10MHz/100MHz вход/выход часов | Питание :12VDC |

| Внутренняя память: PS 4xDDR4(1GB,16bit,2400MT/s) PL4xDDR4(1GB,16bit,2400MT/s) PLB4×DDR4(1GB,16bit,2400MT/s) PLB4×DDR4(1GB,16bit,2400MT/s | |

| Конечный интерфейс PL:

√4xQSFP 100G оптический интерфейс √ 1xJ30J-74ZKWP7-J |

Конечный интерфейс PS:

√ 1xQSPl flash(256MB,8bit) √ 1×10/100/1000 Ethernet сетевой порт √ 1x USB_JTAG/UART отладочный интерфейс √ 1x Type-C √ 1x MicroSD карта √ 4x TEST_SW √4x TEST_LED √4xGPIO (Примечание: Общий интерфейс 1xJ30)-74ZKWP7-J) |

| Амплитуда: ±0.5 дБ (моно 3 ГГц, после калибровки) | Фаза : ±3° (3 ГГц моно, после калибровки) |