Синтезатор тактовой частоты

Когда говорят о синтезаторах тактовой частоты, многие сразу представляют себе просто стабильный генератор. Но это, пожалуй, самое распространённое упрощение, которое мешает по-настоящему понять, с чем мы работаем. На деле, это скорее целая система управления временными domain, где каждый параметр — от фазового шума до времени установления — становится критичным в конкретном применении. Я часто сталкиваюсь с тем, что разработчики, особенно начинающие, выбирают синтезатор по максимальной частоте выхода, совершенно забывая про такой параметр, как джиттер или возможность гибкой перестройки. А потом удивляются, почему цифровой интерфейс в устройстве работает нестабильно или потребление выше расчётного.

Основная путаница: PLL против DDS

Вот смотрите, часто в проектах возникает дилемма: брать классическую схему на основе петли фазовой автоподстройки частоты (ФАПЧ, PLL) или использовать прямой цифровой синтез (DDS). Мне кажется, тут нет универсального ответа, но есть чёткие границы применимости. PLL-синтезатор, особенно с дробным делителем, хорош, когда нужна чистота спектра и низкий фазовый шум в радиочастотных трактах. Но его скорость перестройки... она часто становится узким местом в системах быстрой коммутации каналов.

Я помню один проект для тестового оборудования, где как раз требовалась быстрая перестройка частоты. Сначала поставили продвинутый PLL от одного известного производителя. Цифры в даташите по джиттеру были прекрасны. Но на практике время установления частоты после команды перестройки составляло несколько сотен микросекунд, что для нашей задачи было неприемлемо. Система не успевала за алгоритмом. Пришлось пересматривать архитектуру.

Тут-то и пригодился опыт работы с компонентами, которые поставляют такие интеграторы, как ООО 'Сиань Циюнь Чжисюнь Электронные Технологии'. Их сила, на мой взгляд, как раз в понимании подобных нюансов на уровне системной интеграции. Они не просто продают чипы, а могут предложить решение, где синтезатор тактовой частоты оптимально встроен в общую схему управления цифровыми и аналоговыми доменами платы. Это важно, когда разрабатываешь сложную плату, и от тактового генератора зависит работа сразу нескольких ASIC или процессоров.

Дьявол в деталях: питание и развязка

Одна из самых коварных проблем, которую часто недооценивают, — это влияние цепей питания на работу синтезатора тактовой частоты. Казалось бы, поставил стабилизатор LDO с низким шумом — и порядок. Но на высоких частотах, особенно когда синтезатор питает, например, высокоскоростной АЦП или ЦАП, любой всплеск по шине питания моментально превращается в дополнительный фазовый шум на выходе. Я видел случаи, когда прекрасный по характеристикам синтезатор выдавал ужасный спектр из-за плохо спроектированной развязки или из-за того, что его посадили на одну шину питания с цифровой нагрузкой, которая создавала броски тока.

Здесь практический совет, который я для себя вынес: всегда выделяй для аналоговой части синтезатора, особенно для VCO (генератора, управляемого напряжением), отдельный стабилизатор, а лучше — полностью изолированную цепь питания. И не жалеть керамических конденсаторов с низким ESR на частотах в сотни мегагерц. Иногда простая замена конденсатора типа X7R на C0G в цепи фильтра петли PLL кардинально улучшала подавление побочных составляющих.

Кстати, на сайте apexpcb-cn.ru я как-то изучал их подход к разводке печатных плат для высокоскоростных устройств. У них в разделе с техническими решениями мелькала мысль, которую я полностью разделяю: проектирование синтезатора тактовой частоты начинается не с выбора микросхемы, а с планирования топологии земли и питания на плате. Это абсолютно верно. Потому что даже идеальная по схемотехнике система будет фонить, если её посадить на плохую 'землю'.

Реальный кейс: интеграция в систему на кристалле (SoC)

Современные тенденции — это миниатюризация и интеграция. Сейчас часто синтезатор тактовой частоты встроен прямо в SoC или в специализированную микросхему. И здесь возникает другой набор проблем. Казалось бы, разработчику чипа стало проще — не нужно возиться с внешними компонентами. Но на деле ты попадаешь в жёсткие рамки, которые заложил производитель чипа. Встроенный PLL может иметь ограниченный диапазон коэффициентов деления или фиксированные опорные частоты.

Был у меня опыт с одним телекоммуникационным процессором. Встроенные синтезаторы не могли выдать нужную нам тактовую частоту для внешнего интерфейса Ethernet с требуемой точностью. Пришлось задействовать внешний синтезатор тактовой частоты с более гибкой настройкой. И вот тут опять встал вопрос о синхронизации и взаимном влиянии. Внешний синтезатор работал от своего опорного генератора, а SoC — от своего. Расхождение между ними, даже минимальное, приводило к периодическим ошибкам в пакетной передаче данных. Решение было неочевидным: мы стали использовать один высокостабильный генератор на оба устройства, а сигнал с него разводили с особой тщательностью, чтобы сохранить целостность фронта.

Такие задачи — это как раз область компетенции компаний-интеграторов. Когда ООО 'Сиань Циюнь Чжисюнь Электронные Технологии' позиционирует себя как создатель синергетической экосистемы промышленной цепочки, я понимаю это именно так: они могут взять на себя проблему согласования разнородных компонентов — от чипа до готового модуля, — чтобы инженер-разработчик получил уже валидированное решение, а не набор потенциально конфликтующих микросхем.

Программирование и управление: тонкости, которых нет в мануалах

Ещё один пласт работы — это программный интерфейс управления синтезатором. Большинство современных микросхем программируются через SPI или I2C. Вроде бы всё просто: загрузил регистры — получил частоту. Но на практике... Во-первых, порядок загрузки регистров часто критичен. Нельзя просто записать новое значение делителя. Нужно сначала перевести синтезатор в определённый режим, чтобы не было 'прыжков' частоты или, что хуже, кратковременных срывов генерации.

Однажды мы 'убили' очень дорогой АЦП именно из-за такого срыва генерации. Синтезатор на короткое время выдал спектр с огромным уровнем побочных составляющих, который пробил входную защиту преобразователя. После этого случая я всегда в драйвер добавляю процедуру 'мягкой' перестройки частоты, даже если в даташите она не описана. Это серия последовательных записей в регистры, которая минимизирует переходные процессы.

Во-вторых, вопросы отладки. Как проверить, что синтезатор действительно выдаёт то, что ты запрограммировал? Осциллографом высокочастотный сигнал с низким джиттером не всегда корректно измеришь. Нужен анализатор спектра или специализированный измеритель джиттера. Не у всех они есть под рукой. Поэтому я всегда при первой возможности вывожу сигнал с синтезатора на тестовую точку на плате — даже если в финальном изделии она не нужна. Это страховка на этапе отладки и тестирования.

Взгляд в будущее и практический вывод

Куда всё движется? На мой взгляд, ключевой тренд — это увеличение интеллекта внутри самого синтезатора. Уже сейчас появляются микросхемы, которые самостоятельно могут мониторить уровень фазового шума и подстраивать параметры петли для его минимизации в реальном времени. Или устройства, которые умеют синхронизироваться с несколькими внешними опорными сигналами, обеспечивая бесперебойность в критических системах.

Но как бы ни развивалась технология, базовые принципы остаются. Синтезатор тактовой частоты — это не чёрный ящик, который можно просто припаять. Это система, чья работа глубоко зависит от окружающей её схемотехники, разводки платы и качества питания. Самый дорогой и совершенный чип можно загубить плохой обвязкой.

Поэтому для сложных проектов я всё чаще вижу смысл обращаться к партнёрам, которые обладают именно комплексными возможностями. Не просто продадут компонент, а помогут встроить его в твоё устройство, учитывая все эти подводные камни. Когда компания, та же ООО 'Сиань Циюнь Чжисюнь Электронные Технологии', говорит об управлении целой экосистемой предприятий в цепочке, это даёт надежду, что они могут закрыть вопрос не на уровне отдельной микросхемы, а на уровне готового функционального узла или даже платы, где синтезатор уже оптимально согласован со всеми соседними компонентами. Это экономит массу времени и нервов на этапе доводки изделия. В конечном счёте, именно такая интеграция и позволяет создавать по-настоящему надёжную и предсказуемую электронику.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

От печатной платы до готового продукта: комплексные решения для производства электроники

От печатной платы до готового продукта: комплексные решения для производства электроники -

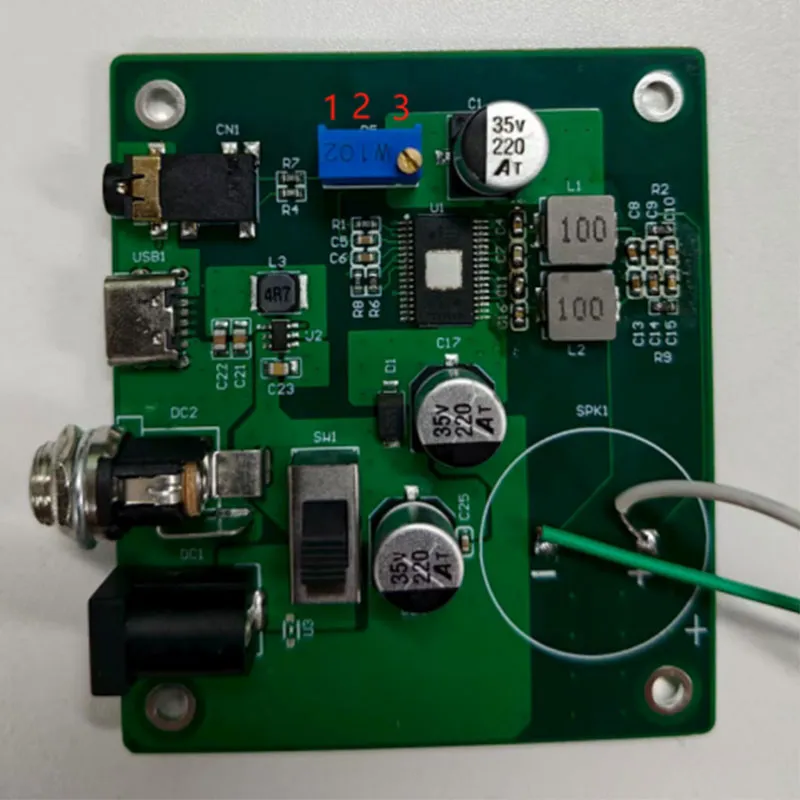

Аудиоусилитель

Аудиоусилитель -

Компьютер QYZX-D20008

Компьютер QYZX-D20008 -

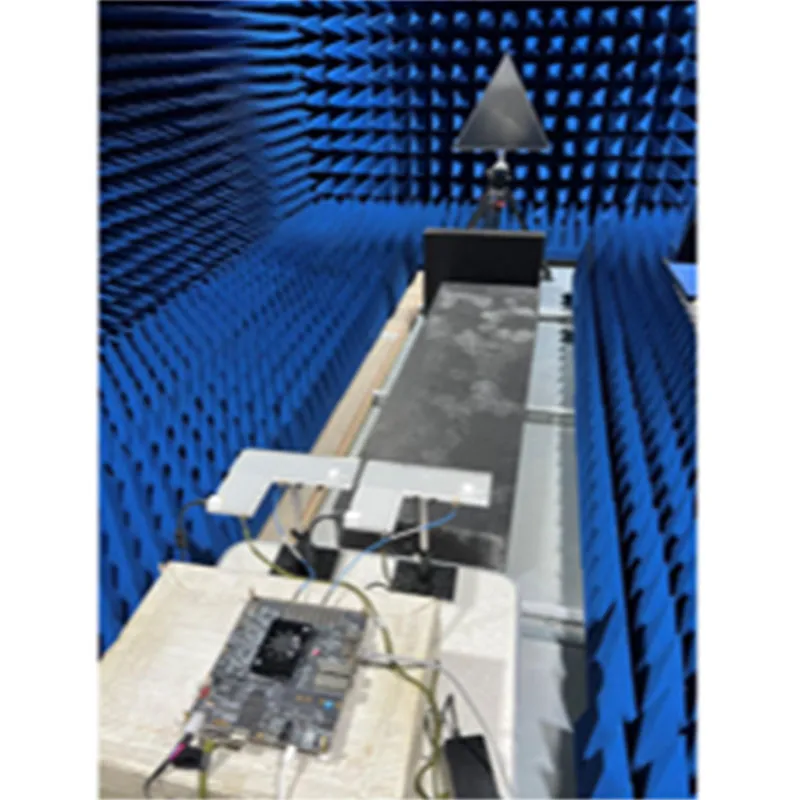

Интегрированная система связи и мониторинга БПЛА в 26 ГГц миллиметровом диапазоне

Интегрированная система связи и мониторинга БПЛА в 26 ГГц миллиметровом диапазоне -

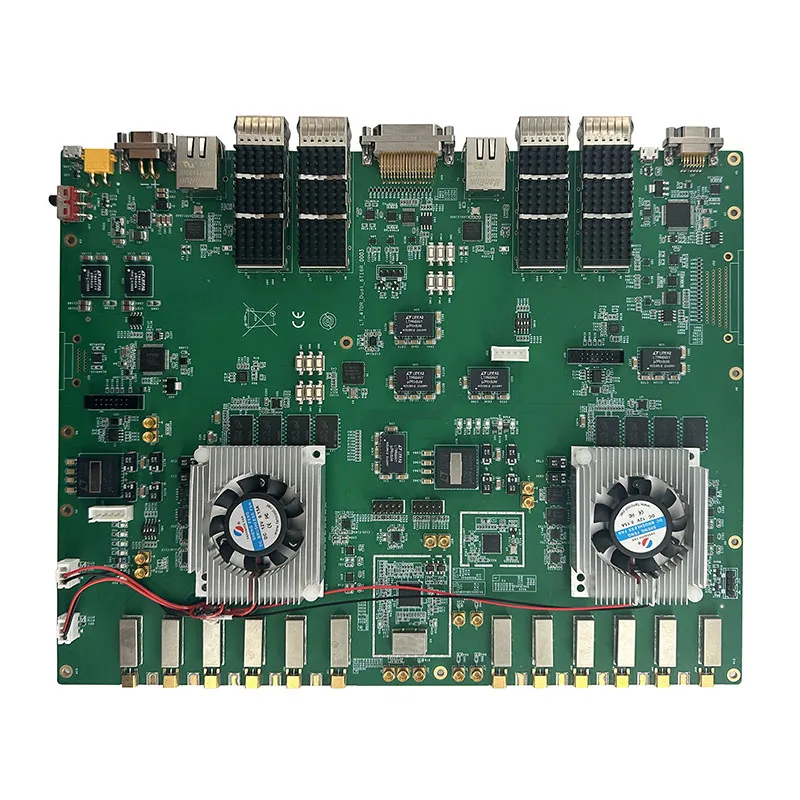

Программно-определяемое радио 4xAD9361

Программно-определяемое радио 4xAD9361 -

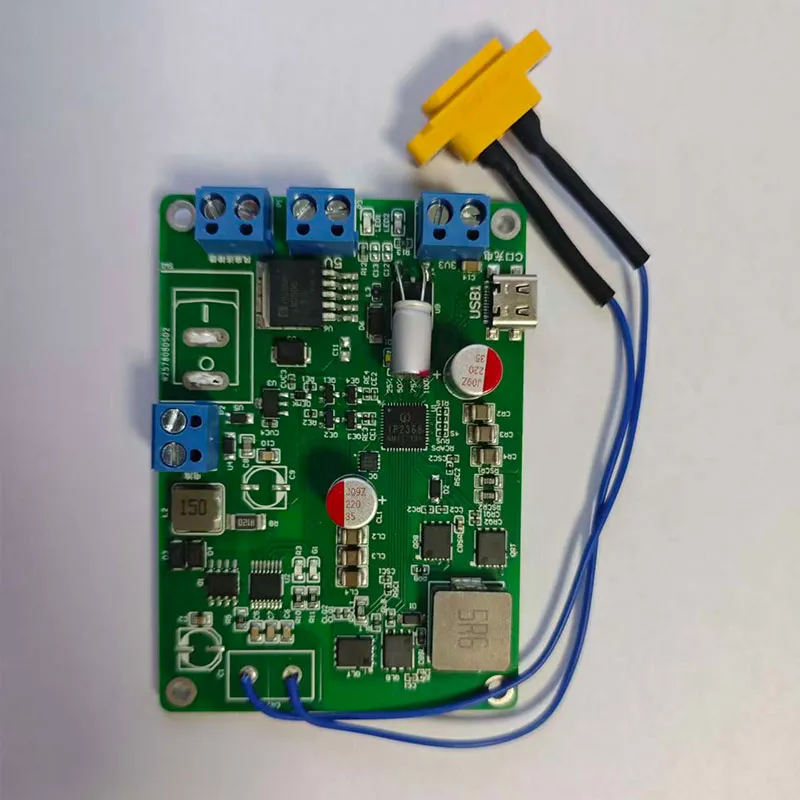

Система солнечной зарядки

Система солнечной зарядки -

4T32R голографическая статическая РЛС

4T32R голографическая статическая РЛС -

Разработка аппаратного обеспечения

Разработка аппаратного обеспечения -

Оптоэлектронная гондола

Оптоэлектронная гондола -

Плата защиты напряжения

Плата защиты напряжения -

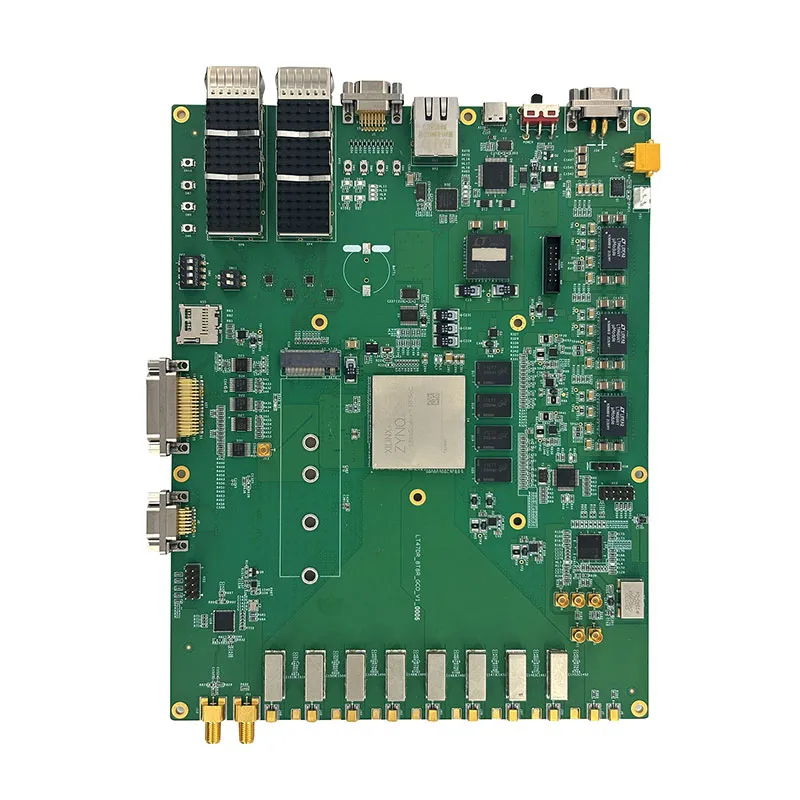

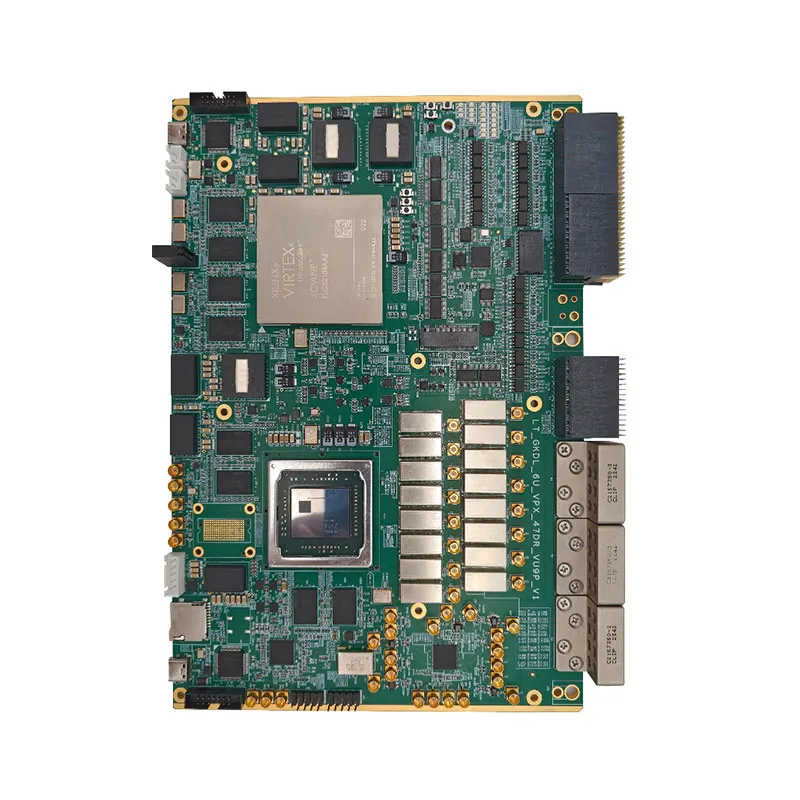

GKDL_6U_VPX_47DR_VU9P_V2

GKDL_6U_VPX_47DR_VU9P_V2 -

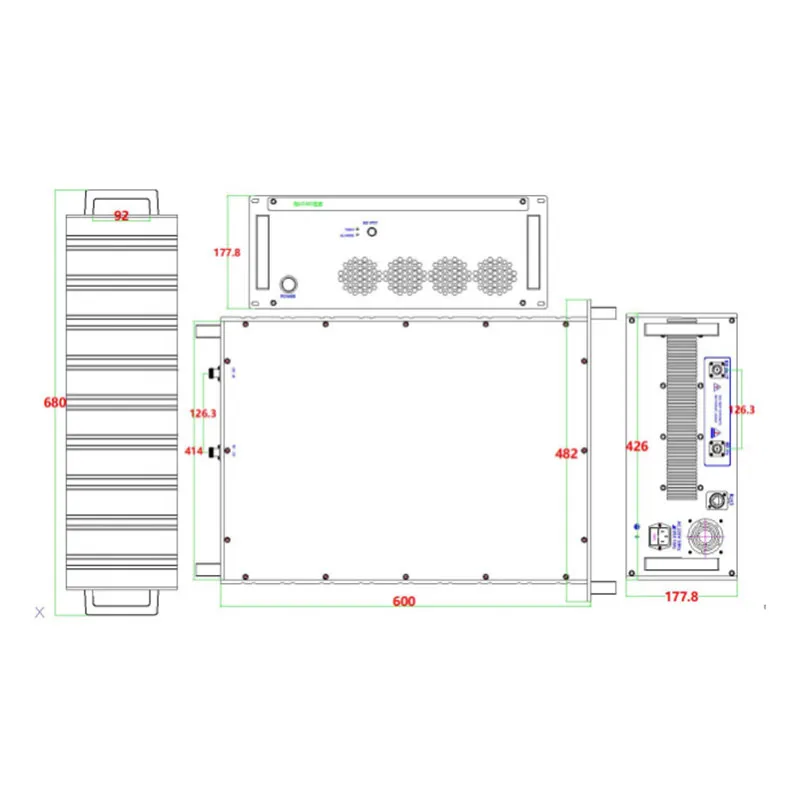

Усилитель мощности PA160-220MHz-500W

Усилитель мощности PA160-220MHz-500W