Прошивка печатных плат

Когда говорят прошивка печатных плат, многие сразу думают о софте — написал код, залил в контроллер, и готово. Но это лишь верхушка. На деле, если ты не чувствуешь саму плату — разводку, помехи, особенности питания — прошивка превращается в кошмар отладки. Видел немало проектов, где программисты винят 'глючное железо', а на деле проблема в непонимании того, как их код взаимодействует с конкретной топологией. Вот об этом и хочу порассуждать — о том, что остаётся за кадром в документации.

Где кроется дьявол: аппаратный контекст прошивки

Возьмём, к примеру, банальный ШИМ на каком-нибудь STM32. В симуляторе всё идеально, на макетке — тоже. А как запаковали в устройство с плотной разводкой, начались сбои. Оказалось, трассировка линии управления к силовому ключу прошла рядом с аналоговой частью — и наводки сказываются на точности таймингов. Прошивка-то одна и та же, но её поведение теперь зависит от того, как плата спроектирована. Приходится в коде вводить задержки, фильтровать чтение состояний — вещи, которые в отрыве от конкретного экземпляра платы неочевидны.

Или другой случай — работа с энергонезависимой памятью по SPI. На отладочном комплекте EEPROM читается стабильно. А на серийной плате, где длина шины увеличена из-за компоновки, уже появляются битые байты. Пришлось лезть в даташит на микросхему и изучать временные диаграммы, чтобы понять: нужно скорректировать настройки делителя частоты в прошивке под возросшую ёмкостную нагрузку. Без понимания паразитных параметров печатного монтажа тут не обойтись.

Поэтому для меня прошивка печатных плат — это всегда диалог с конструктором. Хорошо, когда есть возможность на этапе проектирования обсудить критические узлы: где будет аналоговая земля, как разведены тактовые сигналы, куда поставить дроссели. Потому что потом, когда плата уже изготовлена, многие вещи можно исправить только костылями в коде, что редко идёт на пользу надёжности.

Инструменты и среда: что реально помогает в работе

Много пробовал разных сред отладки. Логически, конечно, удобны сложные комплексы вроде IAR или Keil с их трассировкой. Но в полевых условиях, когда нужно оперативно проверить гипотезу на 'живом' устройстве, часто выручает простенький UART-терминал. Вывод отладочных сообщений в реальном времени — иногда это даёт больше информации, чем фантастические возможности JTAG. Особенно если проблема носит случайный характер и привязана к внешним событиям.

Особняком стоит работа с осциллографом. Для меня это обязательный инструмент при интеграции прошивки и платы. Бывало, смотришь в логи — программа корректно отправляет команду, а на выходе микросхемы — ничего. Подключаешь щупы и видишь, что из-за неправильной инициализации порта в коде формируется неполноценный импульс. Момент 'ага!' наступает именно здесь, а не в тысячах строк кода.

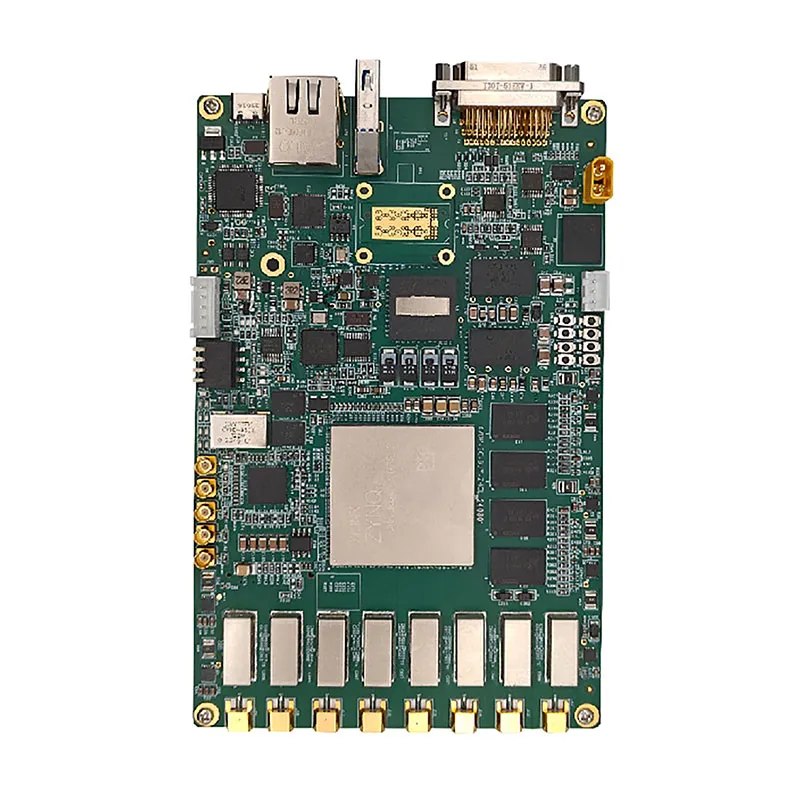

Кстати, о коллегах. Сотрудничал с командой из ООО 'Сиань Циюнь Чжисюнь Электронные Технологии'. Они как раз из тех, кто понимает эту связку. Не просто делают платы под готовый техзадание, а могут с инженерной точки зрения обсудить, как та или иная топология повлияет на будущую прошивку. Их подход к созданию экосистемы — от проектирования до поставки — это как раз про то, чтобы минимизировать такие скрытые проблемы. Когда производитель плат мыслит категориями конечного функционирования устройства, это сильно упрощает жизнь тому, кто будет эту плату 'оживлять' кодом.

Типичные грабли: от которых не застрахован никто

Одна из самых частых ошибок — невнимание к последовательности инициализации периферии в коде. Казалось бы, стандартная процедура: тактирование, порты, потом модули. Но если на плате, например, используется внешний источник опорного напряжения для АЦП, а код сначала включает АЦП, и только потом подаёт питание на этот источник — получаем нестабильные замеры. И ищешь потом ошибку в алгоритме фильтрации, а она — в паре строк кода, которые стоят не в том порядке.

Другая история — работа с прерываниями. Насыщенная событиями система может 'захлёбываться'. Добавил в прошивку обработчик прерывания по приходу данных по USART, а потом заметил, что проседает отклик на управление по I2C. Причина — длительная обработка в прерывании блокирует более приоритетные задачи. Пришлось перекраивать архитектуру, выносить обработку в основной цикл. Это тот случай, когда прошивка написана корректно с точки зрения синтаксиса, но нежизнеспособна в реальных условиях конкретной аппаратной платформы.

И, конечно, вечная тема — энергопотребление. Режимы сна, остановки, пробуждения. Здесь без изучения errata на микроконтроллер и замеров потребления готовой платы вообще делать нечего. Однажды потратил неделю, пытаясь добиться заявленных микроампер в режиме сна. Оказалось, в схеме был pull-up резистор на одной из линий, который я в прошивке не перевёл в Hi-Z состояние. Мелочь, а последствия огромные.

Мысли о процессе: как не утонуть в деталях

Со временем вырабатывается некий алгоритм действий. Сначала — минимальный код, который проверяет жизнеспособность платы: подача питания, сброс, работа тактового генератора. Потом — поэтапное включение модулей, с обязательной проверкой на осциллографе или логическом анализаторе. И только потом — наращивание функционала. Пытаться сразу написать всю прошивку и залить её на чистую плату — путь к многочасовому отчаянию.

Очень выручает ведение простого протокола тестирования. Не какой-то официальный документ, а просто заметки: какая версия кода, что проверял, что наблюдал. Когда через месяц возвращаешься к проекту, эти записи спасают от повторения уже пройденных шагов. Особенно если плат несколько ревизий.

И главное — не стесняться возвращаться к схеме и даташитам. Часто решение проблемы лежит не в области оптимизации алгоритма, а в правильном использовании какого-нибудь бита в регистре настройки, который изначально упустил из виду. Прошивка печатных плат — это дисциплина на стыке, требующая постоянного переключения контекста между 'мягким' и 'твёрдым'.

Вместо заключения: о чём стоит помнить всегда

Никакая, даже самая совершенная прошивка, не сработает корректно на плохо спроектированной или плохо изготовленной плате. И наоборот — отличная 'железная' основа может быть загублена неадекватным кодом. Это паритет. Поэтому, когда видишь компании вроде упомянутой ООО 'Сиань Циюнь Чжисюнь Электронные Технологии', которые делают акцент именно на интеграции и создании полной экосистемы, понимаешь — они движутся в верном направлении. Их опыт, накопленный с 2018 года в инновациях в области электронных схем, как раз про этот системный подход.

В конечном счёте, успех проекта определяется тем, насколько тесно взаимодействуют разработчик схемы, производитель плат и инженер, пишущий прошивку. Когда каждый понимает ограничения и возможности смежных этапов, результат получается стабильным и предсказуемым. А это, пожалуй, и есть главная цель в нашей работе.

Так что, если берёшься за прошивку печатных плат, готовься погрузиться не только в IDE, но и в мир вольт, ампер и наносекунд. Без этого — никуда.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

RT-47DR-AGX-V1

RT-47DR-AGX-V1 -

Обучение разработке на ПЛИС (FPGA)

Обучение разработке на ПЛИС (FPGA) -

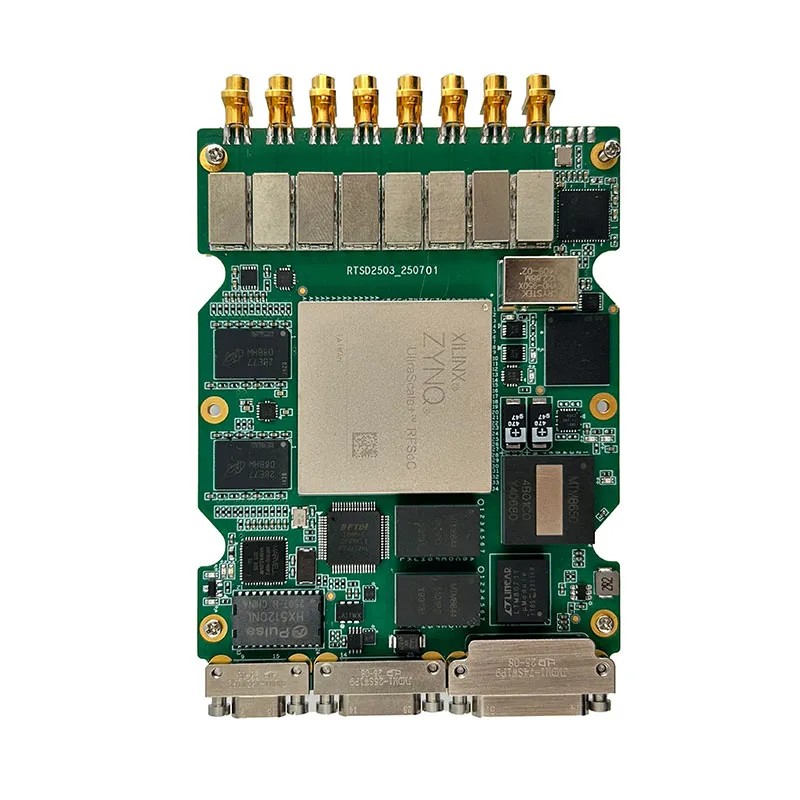

47DR_RTSD2503

47DR_RTSD2503 -

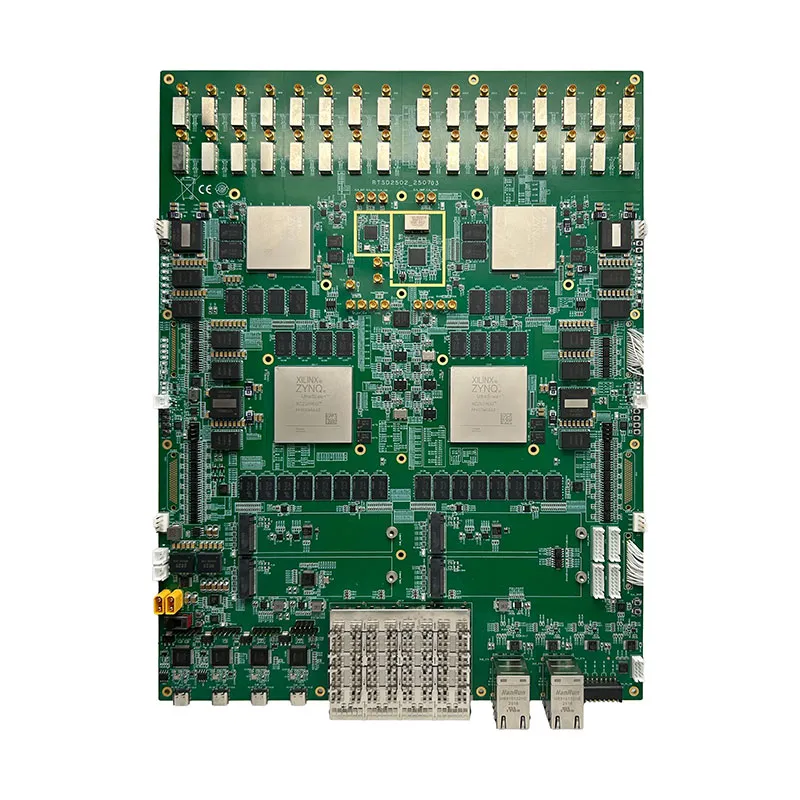

RTSD2502_250703

RTSD2502_250703 -

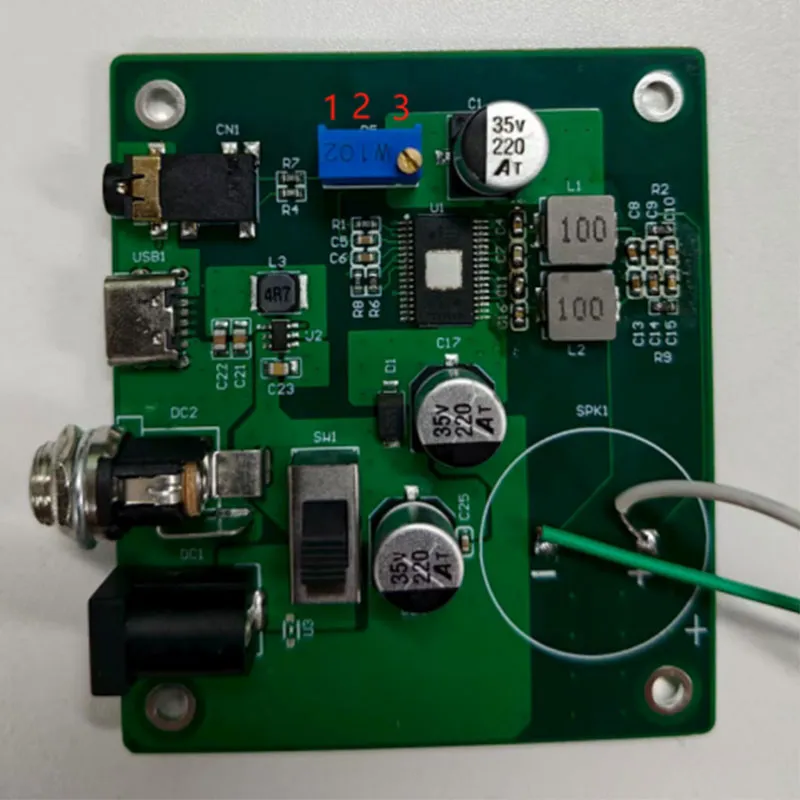

Аудиоусилитель

Аудиоусилитель -

SYNC_V2

SYNC_V2 -

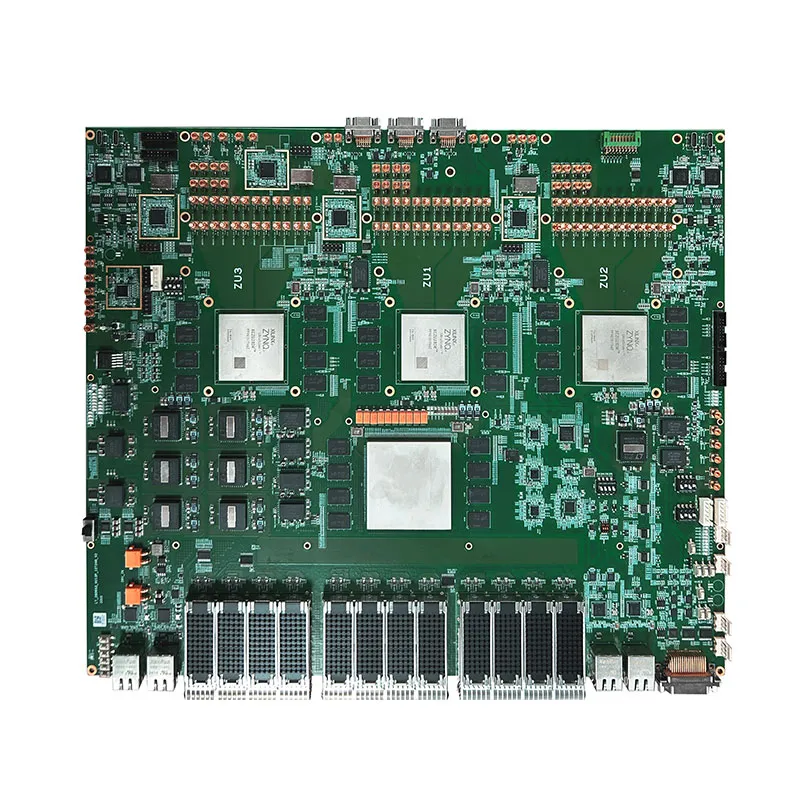

28DRx3_VU13P_9T24R

28DRx3_VU13P_9T24R -

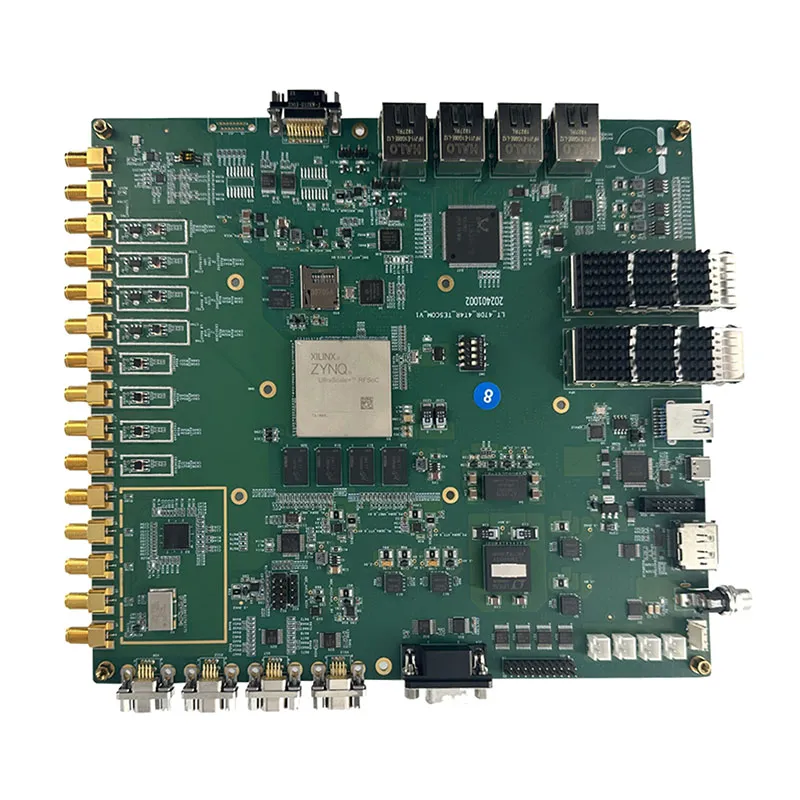

47DR_4T4R_TESCOM_V1

47DR_4T4R_TESCOM_V1 -

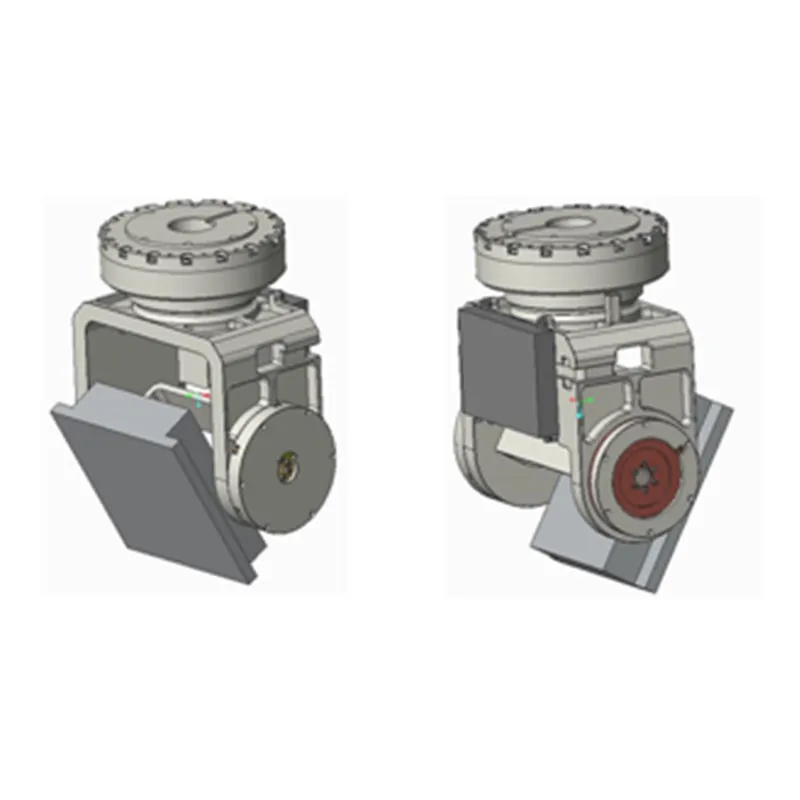

Бортовая РЛС Ka-диапазона

Бортовая РЛС Ka-диапазона -

Высокоскоростной сбор и хранение данных: Прямая запись FPGA в NVMe SSD (восьмидисковый отсек)

Высокоскоростной сбор и хранение данных: Прямая запись FPGA в NVMe SSD (восьмидисковый отсек) -

От печатной платы до готового продукта: комплексные решения для производства электроники

От печатной платы до готового продукта: комплексные решения для производства электроники -

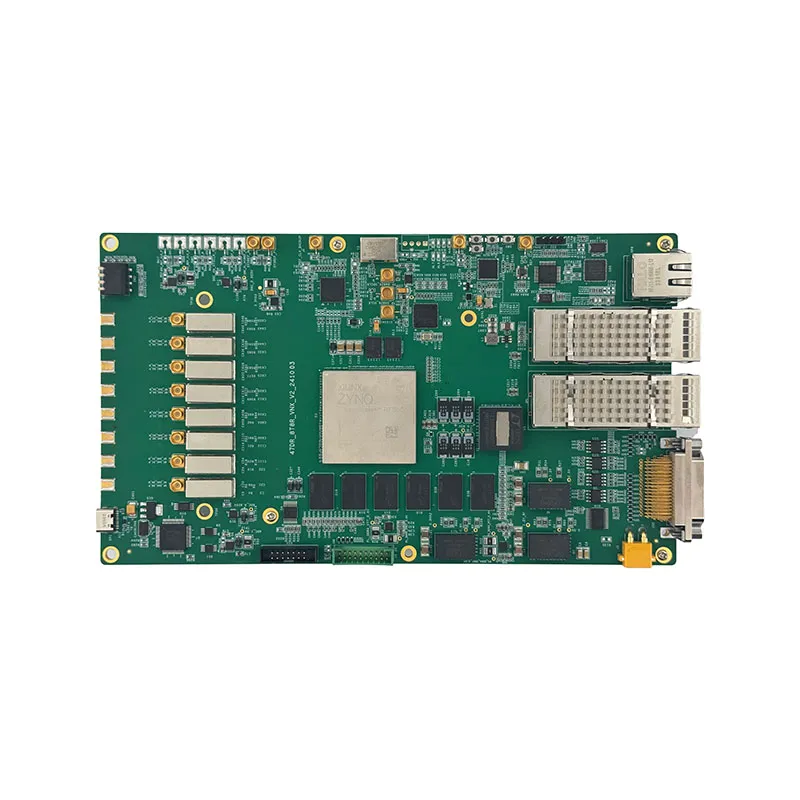

47DR_8T8R_VNX_V2

47DR_8T8R_VNX_V2