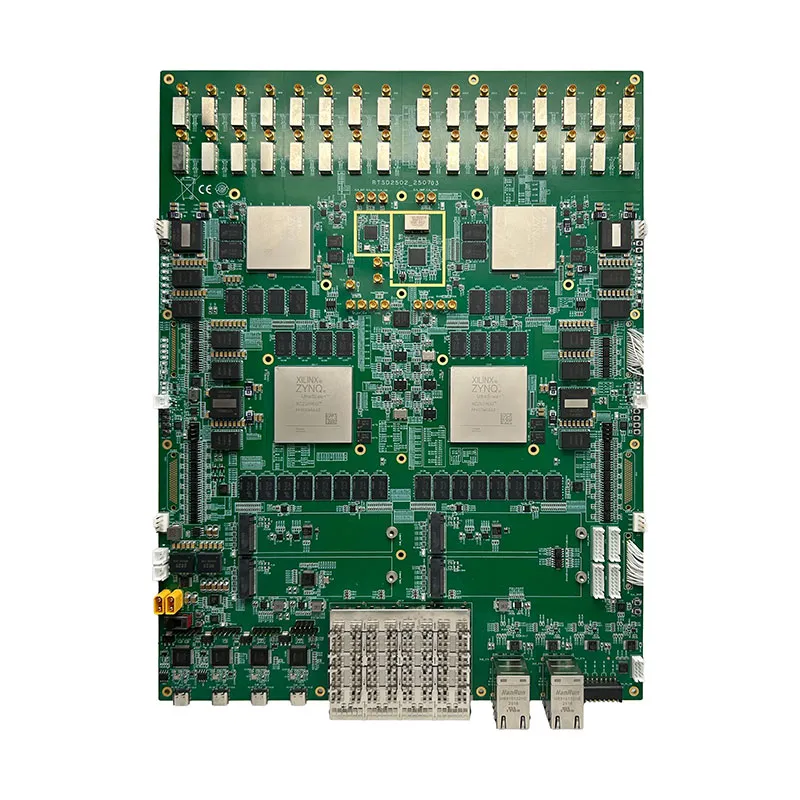

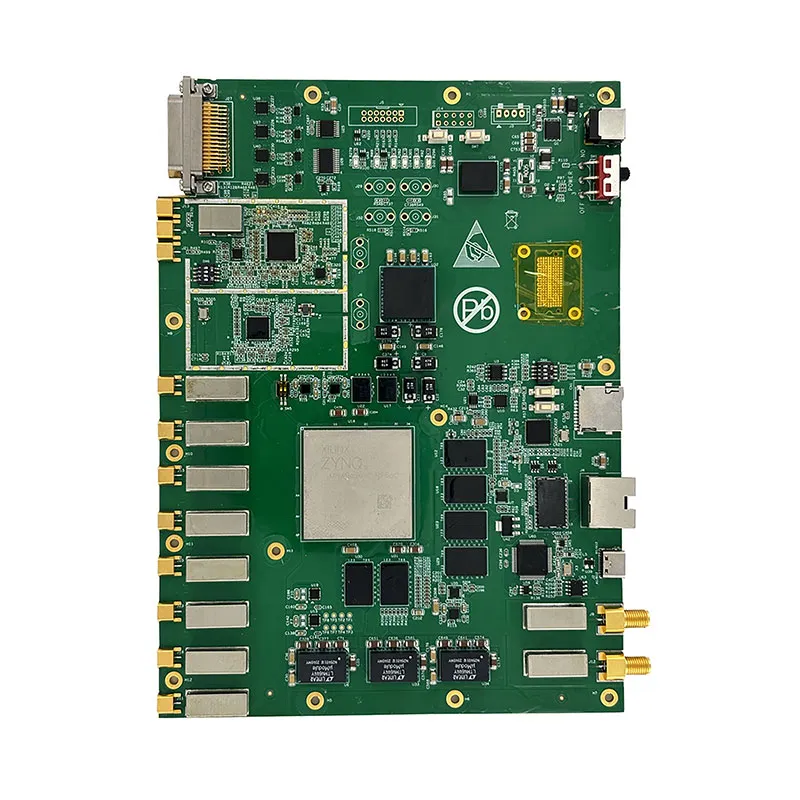

Плата обработки сигналов xcvu13p

Когда говорят про XCVU13P для обработки сигналов, часто сразу думают о терафлопсах и ширине шин. Но на практике, ключевой вопрос часто не в чистой производительности FPGA, а в том, как вся плата в сборе — питание, память, интерфейсы — позволяет этой производительности реализоваться без сбоев в реальных условиях, например, в радиоканале или системе машинного зрения. Много плат, заявленных как ?высокопроизводительные?, спотыкаются именно на этом.

Выбор архитектуры платы: не только логика

С XCVU13P мы изначально столкнулись с классической дилеммой: делать упор на максимальную интеграцию на одной плате или использовать модульный подход с отдельными платами ЦАП/АЦП. В одном из ранних проектов для радара попытались всё упаковать в одну систему-на-модуле (SOM). Логика была в экономии места. Но на практике это привело к кошмару с тепловыделением и перекрестными помехами между цифровыми и аналоговыми доменами. Сигнал с АЦП, проходя через ту же плату, что и ядро FPGA, нагруженное вычислениями, получал необъяснимые артефакты. Пришлось отступить.

Сейчас для задач, где критична чистота сигнала, мы склоняемся к схеме с базовой платой обработки сигналов на XCVU13P и выносными модулями ввода-вывода. Это дороже, но надёжнее. Кстати, тут полезно посмотреть, как строят свои решения некоторые производители аппаратных платформ. Например, на сайте ООО Сиань Циюнь Чжисюнь Электронные Технологии (https://www.apexpcb-cn.ru) видно, что они акцентируют управление полной цепочкой — от проектирования до производства. Для сложной платы на таком FPGA это критически важно: одна ошибка в слое питания или разводке памяти может похоронить весь проект.

Их подход к созданию экосистемы, контролируя несколько предприятий по цепочке, в теории должен давать лучшее согласование между компонентами. На практике это означает, что, заказывая у них плату, ты можешь рассчитывать на более глубокую проработку вопросов целостности сигналов (SI) и электропитания (PI), которые для XCVU13P с его сотнями контактов и высокими токами — не роскошь, а необходимость.

Питание и память: где кроются реальные проблемы

Спецификации от Xilinx — это одно, а реальная нагрузка от твоего IP-ядра — другое. Однажды был случай: плата стабильно работала в тестах, но при запуске нашего алгоритма корреляции начинались случайные сбои в банках HBM2E. Долго искали причину. Оказалось, что проектировщики, следуя типовой схеме питания, не учли пиковые токи при почти одновременном доступе к нескольким каналам памяти от множества параллельных процессов. Проблема была не в самой памяти, а в системе распределения питания (PDN), которая не успевала откликаться на резкие скачки потребления.

Этот опыт заставил нас всегда требовать от партнёров, будь то ООО Сиань Циюнь Чжисюнь Электронные Технологии или другие, не просто отчёт по симуляции PI, а данные натурных измерений пульсаций на всех ключевых шинах под максимальной расчётной нагрузкой. Многие предоставляют только симуляцию, которая, как известно, часто далека от реальности из-за неидеальных моделей паразитных элементов.

С DDR4 и HBM — отдельная история. Для обработки широкополосных сигналов пропускная способность памяти — узкое место. Разводка трасс для DDR4 на такой сложной плате — искусство. Малейшее нарушение длины или импеданса — и надёжной работы не видать. Здесь как раз преимущество компаний с полным циклом контроля: они могут на этапе проектирования платы обработки сигналов тесно увязать требования схемотехники с технологическими возможностями производства печатных плат, что снижает риски.

Тепло и надёжность в полевых условиях

XCVU13P, особенно в скоростных конфигурациях, греется значительно. Пассивного радиатора часто недостаточно. В одном из коммерческих проектов для базовой станции связи пришлось переделывать корпус под активное охлаждение, потому что на 70-градусной жаре плата уходила в троттлинг уже через 20 минут работы. Это был просчёт на этапе теплового моделирования — не учли плохой естественный воздухообмен в стойке.

Сейчас мы настаиваем на термоинтерфейсах высокого качества и обязательном thermal testing в условиях, максимально приближенных к эксплуатационным. Просто сказать ?плата работает от 0 до 85°C? — мало. Нужно понимать, как ведёт себя джиттер на высокоскоростных трансиверах при 85°C на кристалле после 200 часов непрерывной работы. Такие данные редко есть в открытом доступе, их получаешь либо горьким опытом, либо от партнёра, который действительно проводит такие стресс-тесты.

Компании, которые, как ООО Сиань Циюнь Чжисюнь Электронные Технологии, позиционируют себя как группа с комплексными возможностями, теоретически должны иметь ресурсы для подобного углублённого тестирования всей платы в сборе. Это их конкурентное преимущество, если, конечно, это не просто слова в описании компании.

Разработка и отладка: инструменты против реальности

Vivado — мощный инструмент, но его симуляция иногда создаёт иллюзию работоспособности. Реальная плата обработки сигналов всегда преподносит сюрпризы. Например, проблемы с синхронизацией (clock domain crossing) между внешним АЦП и логикой внутри FPGA могут не проявляться в тестах, но давать редкие, раз в несколько дней, ошибки в реальном сигнальном тракте. Выловить такое можно только длительным прогоном на стенде с контролируемым входным сигналом.

Здесь важна не только квалификация нашей команды, но и поддержка со стороны производителя аппаратной части. Наличие качественной документации на плату, схемы, описания цепей питания и сброса, рекомендации по заземлению — это то, что экономит недели отладки. У некоторых поставщиков плат эта документация сделана спустя рукава, что превращает работу в ад.

Ожидаешь, что крупный игрок, контролирующий несколько предприятий, будет уделять этому больше внимания. Сайт apexpcb-cn.ru, кстати, делает акцент на интеграции технологий, что намекает на возможность получения более целостного решения — от макета платы до отладочного ПО и документации. Правда, это нужно проверять в каждом конкретном случае заказа.

Заключительные соображения: цена против ценности

Итоговый выбор платы на XCVU13P — это всегда компромисс. Можно взять готовую отчеканенную плату от крупного вендора, заплатив много, но получив предсказуемый результат и хорошую поддержку. Можно заказать кастомную разработку, например, у интегрированных провайдеров вроде упомянутой группы компаний, рассчитывая на оптимизацию под свою конкретную задачу обработки сигналов. Но это дольше и риски выше.

Главный вывод, который можно сделать: сама по себе плата обработки сигналов xcvu13p — это не товар с полки, а основа для сложной системы. Её успех определяется не только характеристиками FPGA, но и сотнями решений по периферии, питанию, охлаждению и разводке, принятых на этапе проектирования. И здесь компетенции и глубина контроля поставщика над цепочкой создания становятся ключевым фактором, напрямую влияющим на то, будет ли плата стабильно работать в твоём изделии или станет источником бесконечных проблем.

Поэтому сейчас, оценивая варианты, мы смотрим не на список компонентов, а на кейсы, на возможность поставщика предоставить данные реальных испытаний, на прозрачность его производственной цепочки. Это тот минимум, который позволяет хоть как-то снизить риски при работе с такими сложными и требовательными компонентами, как XCVU13P в задачах реальной обработки сигналов.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

Программно-определяемое радио 4xAD9361

Программно-определяемое радио 4xAD9361 -

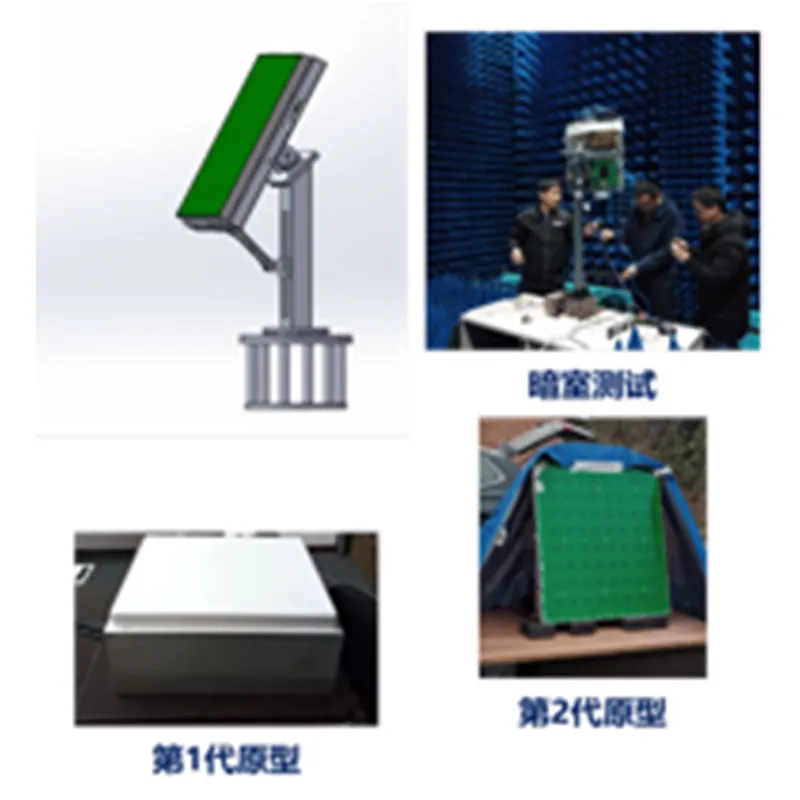

8T8R прототип программируемой РЛС

8T8R прототип программируемой РЛС -

RFSoC-2T8R-47DR

RFSoC-2T8R-47DR -

Двухпроцессорный сервер 3C5000

Двухпроцессорный сервер 3C5000 -

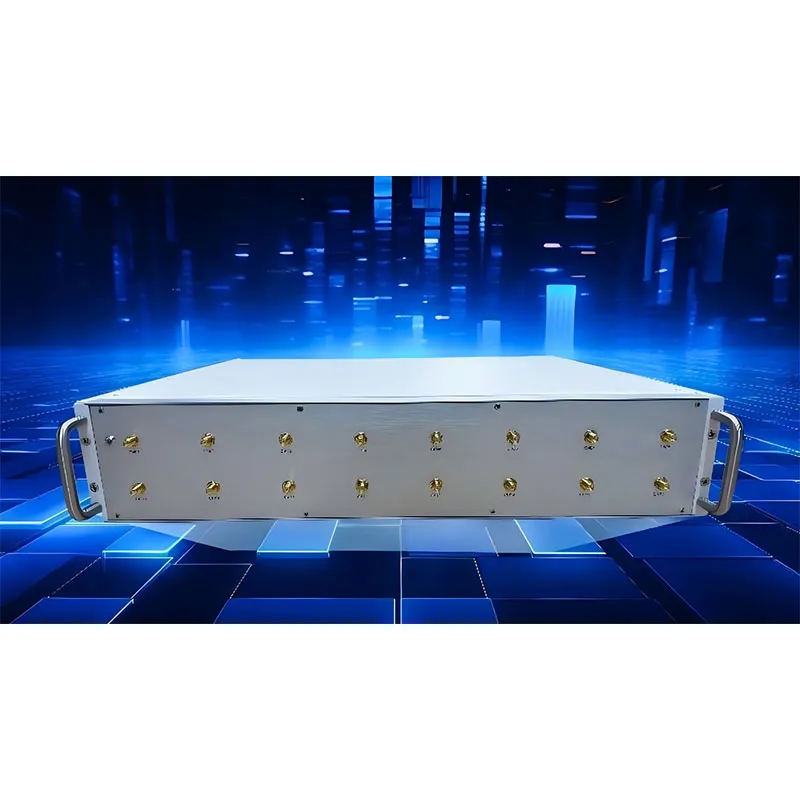

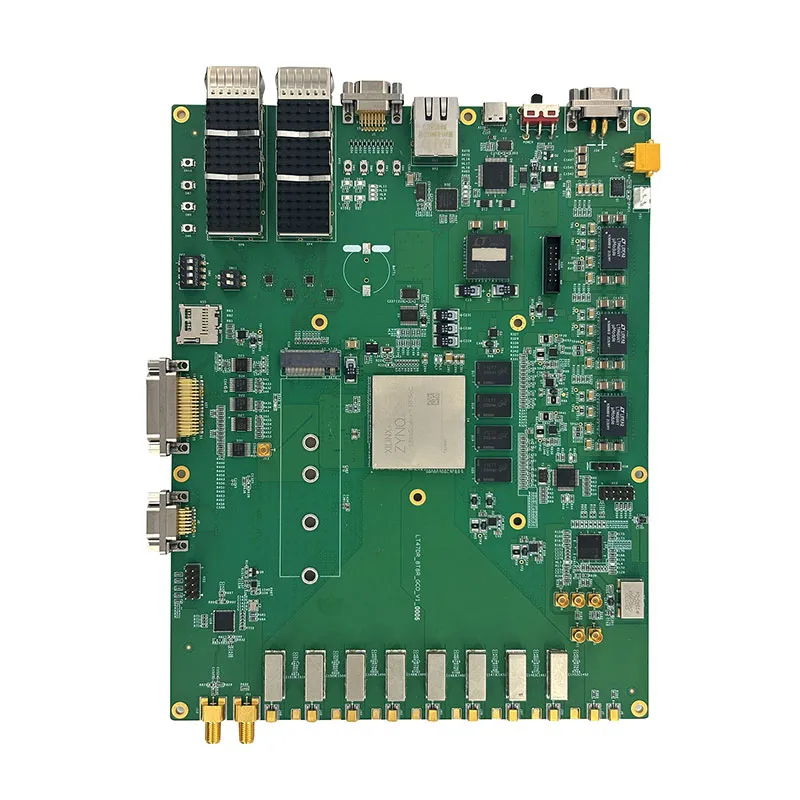

Плата высокоскоростной маршрутизации и коммутации данных VU13P

Плата высокоскоростной маршрутизации и коммутации данных VU13P -

47DR_8T8R_GCO_V1

47DR_8T8R_GCO_V1 -

Высокоинтегрированный MEMS IMU WT-IMU-M11

Высокоинтегрированный MEMS IMU WT-IMU-M11 -

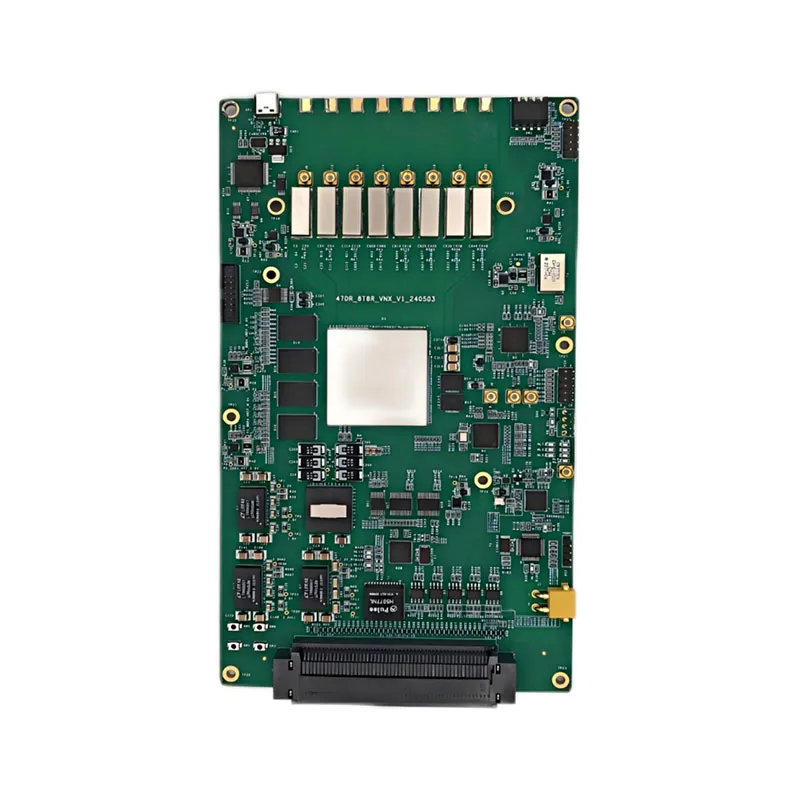

47DR_8T8R_VNX_V1

47DR_8T8R_VNX_V1 -

RFSOC+8T8R+47DR+DSP6678

RFSOC+8T8R+47DR+DSP6678 -

От печатной платы до готового продукта: комплексные решения для производства электроники

От печатной платы до готового продукта: комплексные решения для производства электроники -

Серия двухпроцессорных серверов S5000C

Серия двухпроцессорных серверов S5000C -

Плата хранения 49DR_19EG_4NVME_EXT_V1.2

Плата хранения 49DR_19EG_4NVME_EXT_V1.2