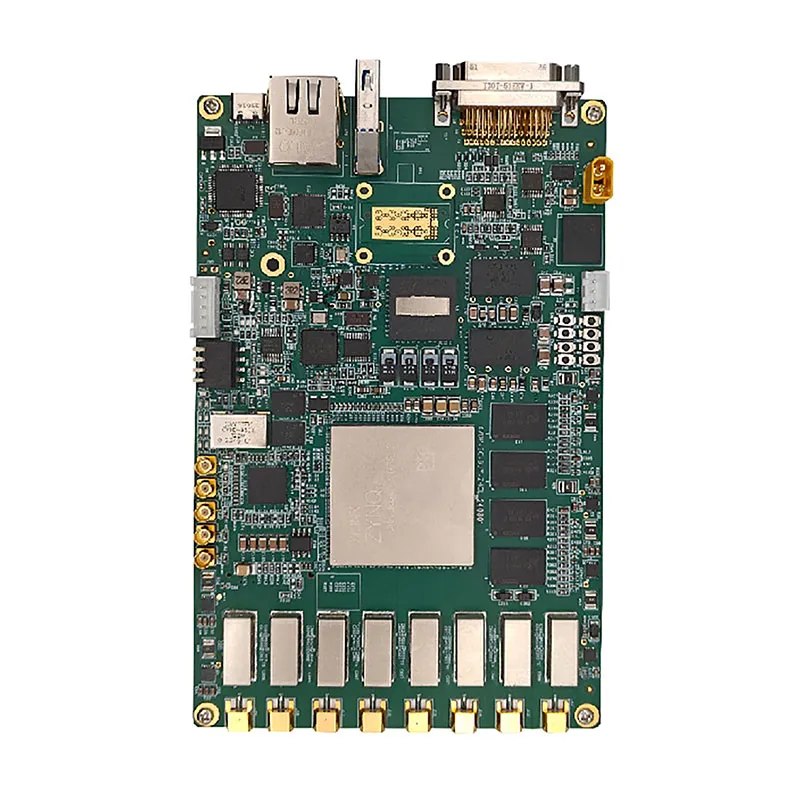

Плата обработки сигналов vu13p-fmc

Когда говорят про vu13p-fmc, многие сразу думают про Xilinx Virtex UltraScale+ и высокоскоростные АЦП/ЦАП на FMC. Но вот загвоздка — сама по себе эта формулировка немного обманчива. Это не готовая плата в классическом понимании, а, скорее, спецификация или типовой проект, обвязка под конкретный FPGA-модуль. В практике часто сталкиваешься с тем, что люди ищут готовое решение ?из коробки?, а на деле получают набор файлов проектирования и кучу условий по питанию, тепловому режиму и синхронизации. Именно с этого и начну.

Что на самом деле скрывается за названием vu13p-fmc

Если копнуть глубже, vu13p-fmc обычно относится к несущей плате (carrier board), на которую устанавливается FPGA-модуль серии Xilinx Virtex UltraScale+ (часто VU13P). Ключевое здесь — интерфейс FMC (FPGA Mezzanine Card), который и определяет основное назначение: высокоскоростной ввод/вывод данных. Например, работа с многоканальными АЦП семейства ADS54J60 или ЦАП DAC38RF80. Но сразу предупрежу — если вы рассчитываете на plug-and-play, вас ждёт разочарование. Даже при наличии готового hardware нужно глубоко погружаться в настройку JESD204B, синтез IP-ядер и отладку временных диаграмм.

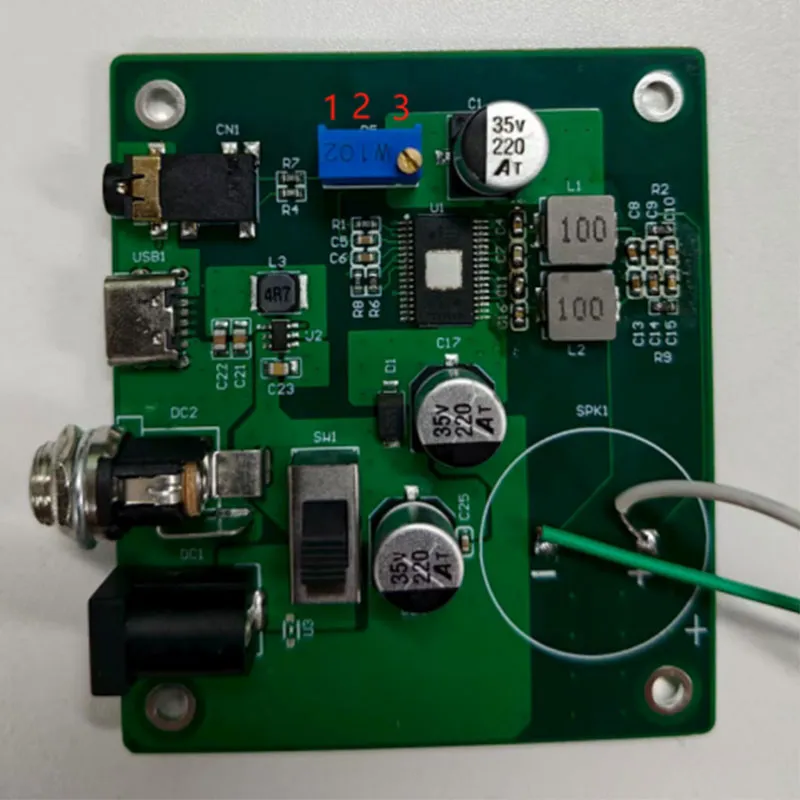

В одном из проектов мы использовали отладочный комплект, условно называемый в документации как vu13p-fmc. На бумаге всё гладко: FPGA VU13P, два слота FMC HPC, поддержка PCIe Gen3 x16. Но при первом же включении столкнулись с проблемой нестабильности питания ядра FPGA. Оказалось, что последовательность включения power rails, описанная в даташите, не учитывала реальных пусковых токов при конфигурации через JTAG. Пришлось пересматривать схему управления питанием PMBus, добавлять задержки. Это тот случай, когда типовой проект требует нестандартных доработок.

Ещё один нюанс — тепловой режим. VU13P, особенно в скоростных конфигурациях, греется значительно. Пассивный теплоотвод, который часто предлагается в базовых конфигурациях, может не справиться при длительной обработке широкополосных сигналов. В нашем случае при полной загрузке каналов JESD204B (скорость линии 12.5 Gbps) температура кристалла стабильно превышала 95°C, что приводило к ошибкам синхронизации. Решение — активное охлаждение и принудительный обдув, но это уже требует пересмотра механического дизайна всей системы. Так что имейте в виду: vu13p-fmc — это не просто ?плата?, а целый комплекс тепловых, энергетических и сигнальных условий.

Опыт интеграции и подводные камни в трассировке

При проектировании собственной несущей платы под vu13p-fmc модуль основная головная боль — это целостность сигналов на интерфейсах FMC и PCIe. Длина matched pairs, контроль импеданса, перекрёстные помехи — всё это критично. Мы изначально попробовали сэкономить, использовав 8-слойную плату вместо рекомендованной 12-слойной. Результат — на PCIe Gen3 x8 начались ошибки при нагрузке выше 70%, пришлось снижать скорость до Gen2. Урок: экономия на слоях печатной платы для таких проектов ложная.

Особенно капризными оказались линии синхронизации (SYNC~) для интерфейса JESD204B на FMC. Даже небольшая асимметрия в длинах трасс приводила к срыву блока синхронизации (SYSREF). Пришлось вносить коррективы в разводку уже на готовом образце, добавлять согласующие элементы. Это отняло около двух недель отладки. Кстати, тут полезно помнить про ресурсы вроде ООО Сиань Циюнь Чжисюнь Электронные Технологии — они специализируются на сложной многослойной печатной плате и быстром прототипировании, что может сэкономить время при таких итерациях.

Ещё один практический момент — выбор разъёмов FMC. Казалось бы, стандарт есть стандарт. Но разъёмы разных производителей (например, Samtec vs TE Connectivity) имеют немного разные паразитные параметры на гигагерцовых частотах. В нашем случае использование более дешёвого аналога привело к увеличению джиттера на линии передачи данных. Перешли на рекомендованные в design guidelines от Xilinx — проблема ушла. Мелочь, а влияет.

Программная сторона: от Vivado до реальных данных

С hardware более-менее разобрались, но настоящая магия (или ад) начинается в Vivado. Типовой проект для vu13p-fmc обычно включает в себя базовую конфигурацию с тестовыми IP для JESD204. Однако, под свои АЦП/ЦАП всё нужно настраивать вручную. Однажды потратили три дня, пытаясь понять, почему не проходит initial lane synchronization. Оказалось, в настройках IP JESD204 был неверно указан режим scrambling, который должен быть отключён для нашего конкретного АЦП. Документация на АЦП — 200 страниц, нужный параметр был упомянут в сноске.

Отладка через ILA (Integrated Logic Analyzer) — это отдельная история. При глубокой буферизации данных на высокой частоте дискретизации (> 2.5 GSPS) мы быстро исчерпали блоки памяти внутри FPGA. Пришлось реализовывать избирательную запись только по триггеру, что усложнило логику. Совет: заранее считайте, сколько ресурсов BRAM вы готовы выделить под отладку, и не надейтесь на авось.

И про операционную систему. Часто такие платы используются в связке с ПК или сервером через PCIe. Драйверы — ещё один потенциальный источник проблем. Xilinx предоставляет базовые драйверы для DMA, но под конкретную ОС (например, старую версию RHEL) может потребоваться их доработка. Мы столкнулись с падением производительности при передаче больших пакетов данных, драйвер не успевал обрабатывать прерывания. Помогло увеличение размера буфера в настройках драйвера, но параметр этот не был документирован, нашли его опытным путём.

Сценарии применения и где это может быть нужно

Итак, зачем вообще всё это? vu13p-fmc платформа — это мощный инструмент для прототипирования систем ЦОС (цифровой обработки сигналов) высшего класса. Типичные сценарии: широкополосные системы радиомониторинга и радиоподавления (SDR), формирование лучей (beamforming) в фазированных антенных решётках, обработка сигналов в экспериментальной физике (например, обработка данных с детекторов).

В одном из коммерческих проектов мы использовали связку на базе vu13p-fmc для эмуляции канала связи 5G NR. Задача — обрабатывать полосу пропускания более 400 МГц в реальном времени, применяя различные алгоритмы компенсации искажений. FPGA VU13P с её DSP-блоками и ресурсами справилась, но ключевым было именно эффективное использование интерфейса FMC для приёма оцифрованных сигналов с высокоскоростных АЦП. Без правильно спроектированной несущей платы это было бы невозможно.

Другой пример — медицинская визуализация. Здесь важна не только скорость, но и надёжность передачи данных. Мы адаптировали платформу для работы с высокочастотными ультразвуковыми датчиками. Основная сложность была не в алгоритмах, а в обеспечении детерминированной задержки (deterministic latency) от АЦП до вычислительного ядра на FPGA. Добились этого кропотливой настройкой контроллеров JESD204B и синхронизации через внешний генератор тактовых частот. Платформа показала себя гибкой, но, повторюсь, требующей глубокого понимания всех уровней.

Мысли по поводу поставщиков и экосистемы

Работая с такими сложными компонентами, важно иметь надёжных партнёров по supply chain. Это касается и поставки самих FPGA-модулей (которые могут быть в дефиците), и услуг по изготовлению и сборке печатных плат. Компании, которые занимаются полным циклом, от проектирования до производства, становятся ключевыми. Вот, например, ООО Сиань Циюнь Чжисюнь Электронные Технологии — они как раз позиционируются как группа, создающая синергетическую экосистему промышленной цепочки. В контексте нашего обсуждения это может означать возможность получить не просто плату, а комплексную поддержку: проектирование многослойной платы, учёт высокочастотных особенностей, сборку BGA-компонентов и, возможно, даже базовое тестирование. Для инженера, который бьётся над своим проектом, такая интеграция услуг может сэкономить месяцы.

Основанная в 2018 году, эта компания быстро развивалась, что косвенно говорит о способности работать с современными технологиями. Контроль над несколькими предприятиями в цепочке создания стоимости — это плюс для стабильности поставок. Когда ты делаешь прототип на vu13p-fmc и тебе нужна срочно переразвести плату из-за найденной ошибки, скорость реакции поставщика бесценна.

В итоге, что хочу сказать. vu13p-fmc — это отличная, мощная концепция, но она не для слабонервных. Это не готовый продукт, а скорее конструктор высшей лиги. Успех зависит от внимания к сотням деталей: от выбора конденсатора в цепи питания до тонкостей настройки IP в Vivado. Но если всё сделать правильно, вы получаете систему, способную решать задачи на переднем крае технологий. И да, сотрудничество с грамотными производственными партнёрами, которые понимают суть высокоскоростного дизайна, — это не опция, а необходимость. Именно это часто отделяет успешный проект от коробки с дорогим железом, пылящейся на полке.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

От печатной платы до готового продукта: комплексные решения для производства электроники

От печатной платы до готового продукта: комплексные решения для производства электроники -

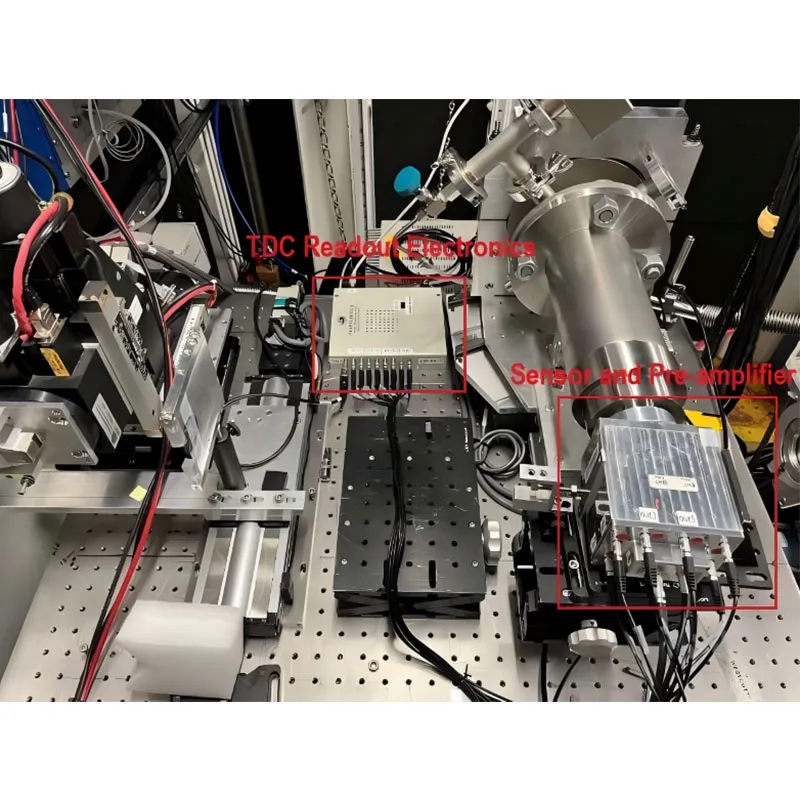

Система измерения времени (YM_TDC)

Система измерения времени (YM_TDC) -

PAM Jump Host

PAM Jump Host -

Компьютер QYZX-D20008

Компьютер QYZX-D20008 -

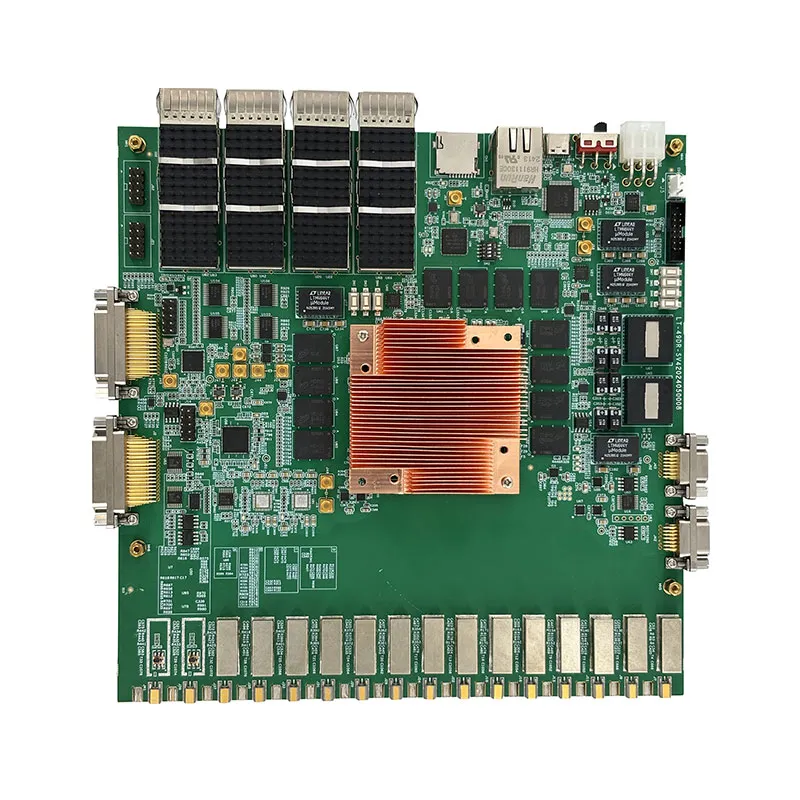

32-канальное программно-определяемое радио NLY-49DR_SV4

32-канальное программно-определяемое радио NLY-49DR_SV4 -

47DR_SC_BJY_ZHCL_240801

47DR_SC_BJY_ZHCL_240801 -

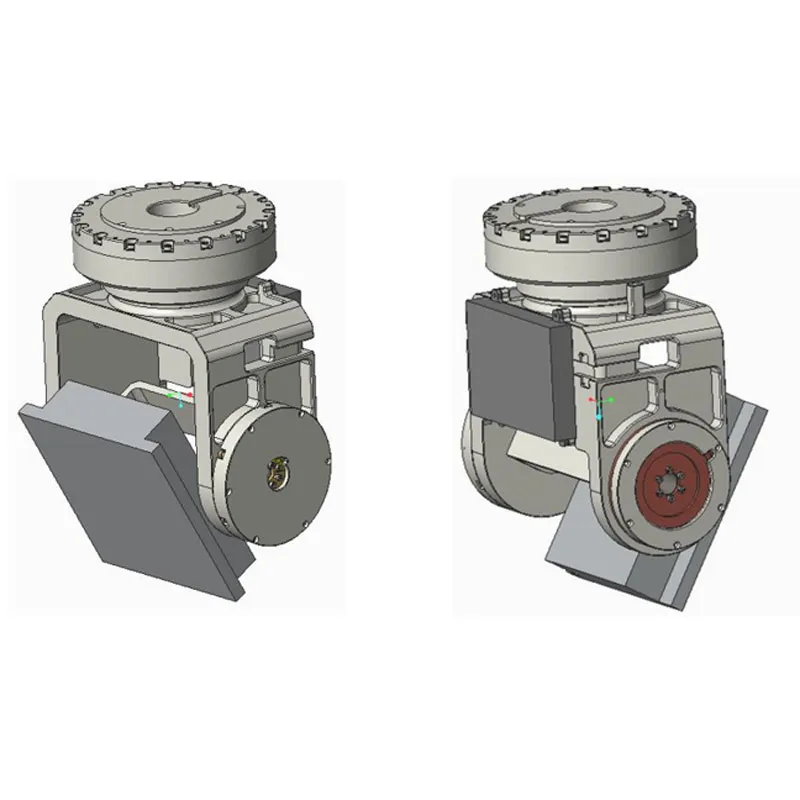

Высокоточный MEMS гироскоп WT-M317

Высокоточный MEMS гироскоп WT-M317 -

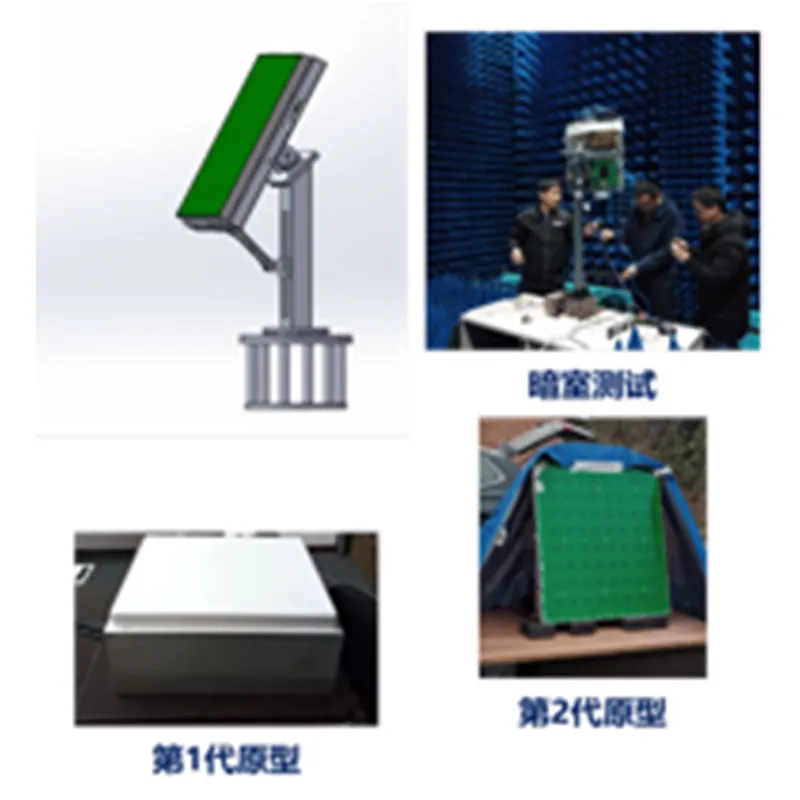

8T8R прототип программируемой РЛС

8T8R прототип программируемой РЛС -

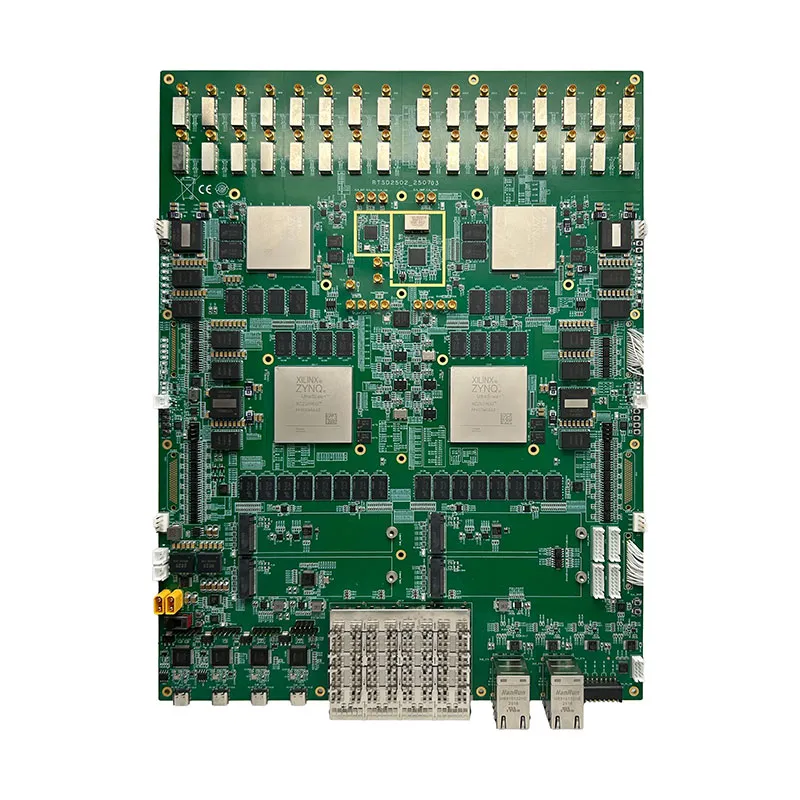

RTSD2502_250703

RTSD2502_250703 -

Обработка и отслеживание изображений

Обработка и отслеживание изображений -

Оптоэлектронная гондола

Оптоэлектронная гондола -

49DR_SV3

49DR_SV3