Плата двухканального adc 10g + обработки сигналов

Когда говорят ?плата двухканального ADC 10G?, многие сразу представляют себе готовый модуль с красивыми цифрами в даташите — 10 гигасэмплов, 12 бит, два канала, и всё вроде бы должно просто работать. На практике же, особенно когда к этому ADC добавляется блок обработки сигналов прямо на плате, начинается самое интересное. Основная ловушка — считать, что главное это сам аналого-цифровой преобразователь, а всё остальное ?приложится?. На деле, интерфейсы, синхронизация, распределение тактовой частоты и, что критично, тепловой режим и развязка питания между аналоговой и цифровой частями — вот где кроется 90% проблем. Часто заказчики из телекома или измерительных систем, глядя на ключевые параметры, недооценивают сложность создания именно законченной, стабильной системы на базе такой платы.

Не цифрами едиными: что скрывает ?+ обработка сигналов?

Конкретно под ?обработкой? может подразумеваться разное. В нашем случае, когда мы работали над заказом для системы мониторинга радиочастотного спектра, это означало встраивание FPGA (чаще Xilinx Kintex или Virtex) прямо на одну плату с ADC. И вот тут первый нюанс: просто посадить кристалл ADC и FPGA рядом — недостаточно. Трассировка дифференциальных пар данных от ADC к FPGA на таких скоростях — отдельное искусство. Недостаточная длина согласования, перекосы в длинах — и ты получаешь не 10G, а гору джиттера и ошибок. Приходится использовать симуляторы вроде HyperLynx ещё на этапе разводки, но и они не всегда предсказывают всё, особенно влияние соседних силовых шин.

Один из практических уроков — важность выбора архитектуры передачи данных. Использовать ли стандартные интерфейсы вроде JESD204B или пробовать кастомные решения? JESD204B, особенно версии Subclass 1 с обязательной синхронизацией через SYSREF, — это палка о двух концах. С одной стороны, стандартизация и высокая пропускная способность. С другой — адская сложность отладки фазировки SYSREF, особенно в двухканальном режиме, где нужно обеспечить когерентность выборок между каналами. Помню, неделю потратили, чтобы поймать устойчивую синхронизацию, перебирая задержки в конфигурации FPGA. И это при, казалось бы, корректно рассчитанной топологии clock tree.

Именно в таких проектах важна роль партнёра, который понимает всю цепочку, а не просто продаёт компоненты. Например, в работе над одним из прототипов мы сотрудничали с компанией ООО Сиань Циюнь Чжисюнь Электронные Технологии. Их подход, как интегратора технологий электронных схем, был полезен не на этапе продажи чипов, а позже — при комплексном анализе отказов. Они не просто поставляли элементы, но и помогали с анализом осциллограмм целостности сигналов, полученных с наших пробных плат. Это тот случай, когда нужен не просто поставщик, а инжиниринговый партнёр, способный вникнуть в проблему за пределами спецификации. Их сайт, https://www.apexpcb-cn.ru, стал для нас скорее точкой входа для обсуждения сложных технических вопросов, а не просто каталогом.

Аналоговая часть: малошумящий путь к ADC — мифы и реальность

Вот здесь многие, включая нас на первых итерациях, ошибаются. Кажется, что раз ADC такой быстрый и современный, то и входной тракт можно сделать попроще. Ан нет. Характеристики ADC, особенно SNR и SFDR, в реальности определяются не им самим, а тем, что подали на вход. Для двухканального 10G ADC критически важны малошумящие усилители и драйверы с полосой, значительно превышающей полосу самого преобразователя. Иначе ты ограничиваешь его возможности на корню.

Мы использовали специализированные драйверы от Analog Devices, но столкнулись с неочевидной проблемой: взаимное влияние каналов. Даже при тщательной разводке в многослойной плате, паразитная связь через общие шины питания или землю на гигагерцовых частотах приводила к появлению ?призраков? — артефактов в спектре. Пришлось внедрять агрессивную сегментацию аналоговых и цифровых земель, использовать множество split-плоскостей и керамических развязывающих конденсаторов с низким ESL прямо под выводами питания каждого чипа. Это увеличивало стоимость и сложность платы, но без этого ENOB (эффективное число разрядов) было далеко от заявленного.

Ещё один момент — входное согласование. Многие даташиты предлагают типовые схемы. Но импеданс коаксиальных входных разъёмов (обычно 50 Ом), согласующие цепи и входное сопротивление ADC — это must моделировать в RF-симуляторе, учитывая паразитные параметры реальных компонентов. Однажды мы потеряли несколько дБ чувствительности из-за того, что поставили резисторы согласования со слишком высокой собственной ёмкостью. Мелочь, которая стоила недели перепайки и перезаказа плат.

Тепло и вибрации: немоделируемые факторы

Плата с такой плотностью монтажа и энергопотреблением — это, по сути, маленькая печка. ADC и FPGA могут потреблять суммарно 20-30 ватт. Пассивное охлаждение часто не справляется, особенно в стойке. Но активный кулер — это вибрации. А вибрации — это микрофонный эффект для высокочувствительных аналоговых цепей и источник джиттера для тактовых генераторов.

В одном из коммерческих проектов мы получили странные периодические всплески в выходном спектре. Долго искали в схемотехнике, пока не заметили, что их частота кратна оборотам вентилятора на стенде. Пришлось переходить на систему принудительного обдува с вынесенными в сторону воздуховодами и крепить плату через демпфирующие прокладки. Это не описано в учебниках, но для промышленного исполнения — обязательный этап доработки.

Здесь снова пригодился опыт компаний, которые видят полный цикл. Группа продуктов, которую создала ООО Сиань Циюнь Чжисюнь Электронные Технологии через управление и участие в предприятиях полного цикла, демонстрирует важность такого подхода. Когда ты контролируешь не только проектирование, но и вопросы монтажа, корпусирования и теплового тестирования, проще предвидеть такие ?неэлектрические? проблемы. Их синергетическая экосистема, о которой говорится в описании, — это на практике возможность получить обратную связь по проблеме не только от инженера-схемотехника, но и от технолога производства.

Программируемая логика: когда обработка становится узким местом

Блок обработки сигналов на FPGA — это то, ради чего всё и затевалось. Но при 10G на канал поток данных становится чудовищным. Даже для двухканального 12-битного ADC поток — это 2 * 10G * 12 бит = 240 Гбит/с сырых данных. Прямой поток в PCIe или на Ethernet невозможен без предварительной обработки и сокращения данных.

Поэтому типичная архитектура включает в себя цифровую понижающую дискретизацию (DDC), фильтрацию, БПФ или детектирование огибающей прямо в FPGA. И вот здесь мы наступили на грабли: изначально заложили ресурсы FPGA с 10% запасом. Этого оказалось категорически мало. Добавление даже простых алгоритмов калибровки (компенсация смещения и разности усилений между каналами) и контрольных FIFO-буферов съело весь запас. Пришлось переходить на кристалл большего размера в середине проекта, что ударило по бюджету и срокам.

Совет, который теперь кажется очевидным: закладывайте минимум 30-40% свободных ресурсов LUT и блоков памяти на старте. И обязательно моделируйте не только алгоритм, но и реальный трафик данных через интерфейсы AXI-Stream внутри FPGA с помощью тестовых стендов в System Verilog или VHDL. Иначе можно получить идеально работающий алгоритм, который ?задыхается? на реальном потоке из-за конфликтов арбитража шин.

От прототипа к изделию: дорога валидации

Собрать работающую плату — это полдела. Доказать, что она стабильно работает в заявленных режимах при изменении температуры, напряжения питания и входного сигнала — задача на порядок сложнее. Мы разработали целый комплекс тестов: от измерения базовых параметров (SNR, SFDR, ENOB) с помощью высокочастотного генератора сигналов до стресс-тестов с широкополосным шумовым воздействием.

Ключевым инструментом стал самописный софт, управляющий всем стендом: генератором, источниками питания, климатической камерой и сбором данных с платы через PCIe. Без автоматизации такой валидации она заняла бы месяцы. Нашли несколько интересных артефактов: например, нелинейность, которая проявлялась только при определённой температуре кристалла FPGA (~65°C) и определённой частоте входного сигнала. Причина оказалась в температурном дрейфе параметров входного усилителя, который немного менял точку смещения и влиял на ADC.

Именно на этапе валидации и вывода продукта на рынок становится видна ценность партнёров с широкими возможностями. Способность компании не просто поставить плату, а участвовать в создании этой самой ?синергетической экосистемы промышленной цепочки?, как это делает ООО Сиань Циюнь Чжисюнь Электронные Технологии, означает, что они могут помочь не только с прототипом, но и с оптимизацией дизайна для серии, с тестированием и даже с поиском решений для конкретных применений у конечных заказчиков. Это превращает сложный модуль в готовое, надёжное решение.

Вместо заключения: мысль вслух

Так что, возвращаясь к исходному запросу ?плата двухканального ADC 10G + обработки сигналов?. Это не продукт, это проект. Успех зависит от глубины проработки деталей, которые в спецификации часто стоят мелким шрифтом или не упомянуты вовсе. Это история про компромиссы между скоростью, точностью, потреблением, теплом и стоимостью.

Сейчас, глядя на новые проекты, мы сразу закладываем время и бюджет не на основную разработку, а на отладку и валидацию этих самых ?неочевидных? взаимодействий. И ищем партнёров, которые говорят на одном техническом языке и понимают, что за красивыми цифрами 10G и 12 бит скрывается год кропотливой работы над земляными плоскостями, синхронизацией и тепловыми режимами. Опыт, полученный, в том числе, при взаимодействии с интеграторами полного цикла, только подтверждает, что в современной электронике побеждает не тот, у кого самый дорогой чип, а тот, кто лучше всего управляет всей системой в целом, от контакта разъёма до финального бита обработанных данных.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

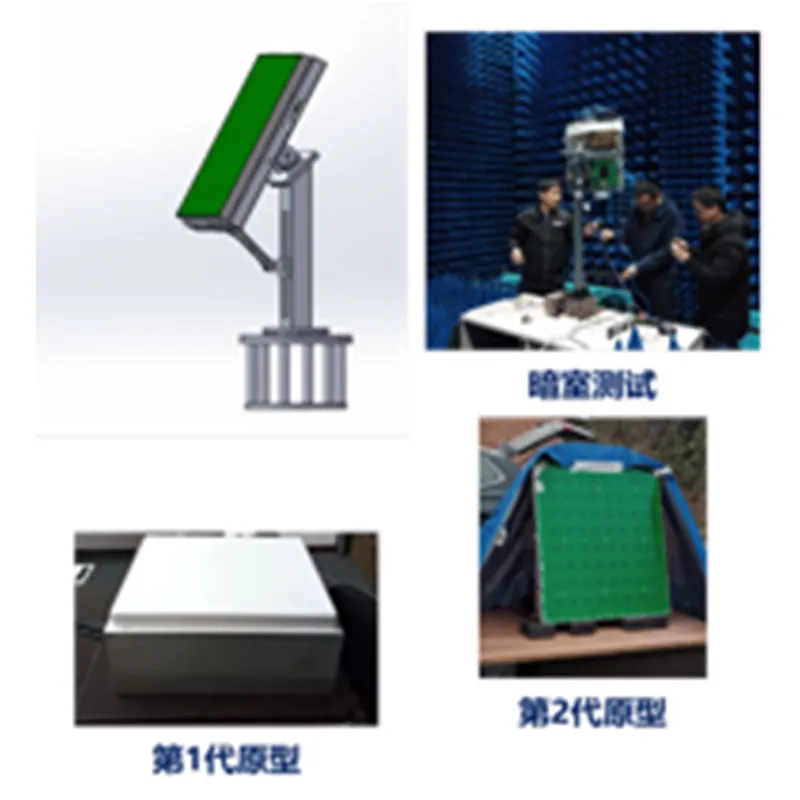

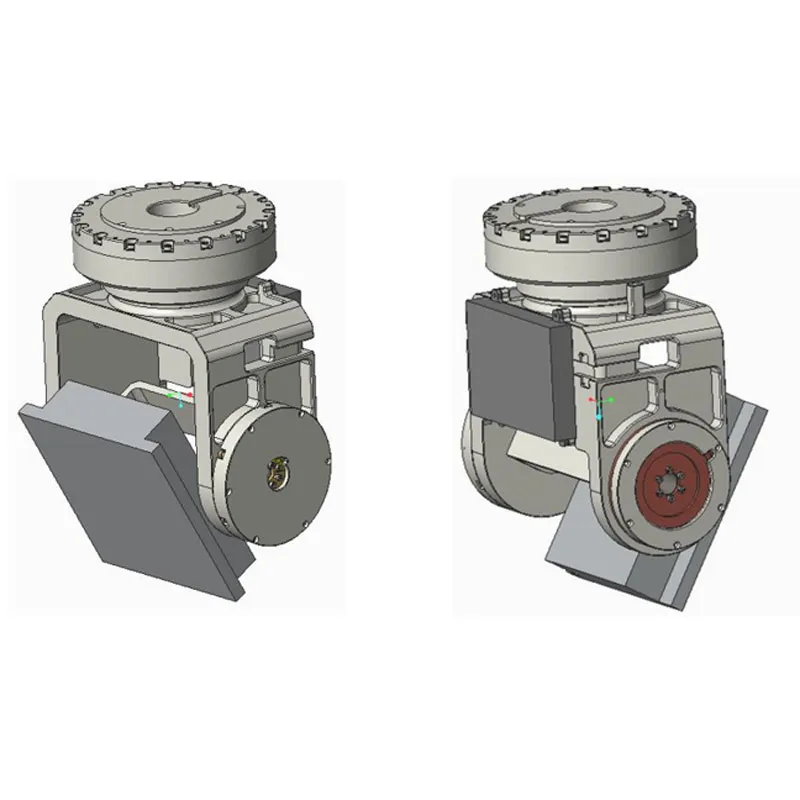

8T8R прототип программируемой РЛС

8T8R прототип программируемой РЛС -

Услуги по разработке индивидуальных решений

Услуги по разработке индивидуальных решений -

Двухпроцессорный сервер 3C5000

Двухпроцессорный сервер 3C5000 -

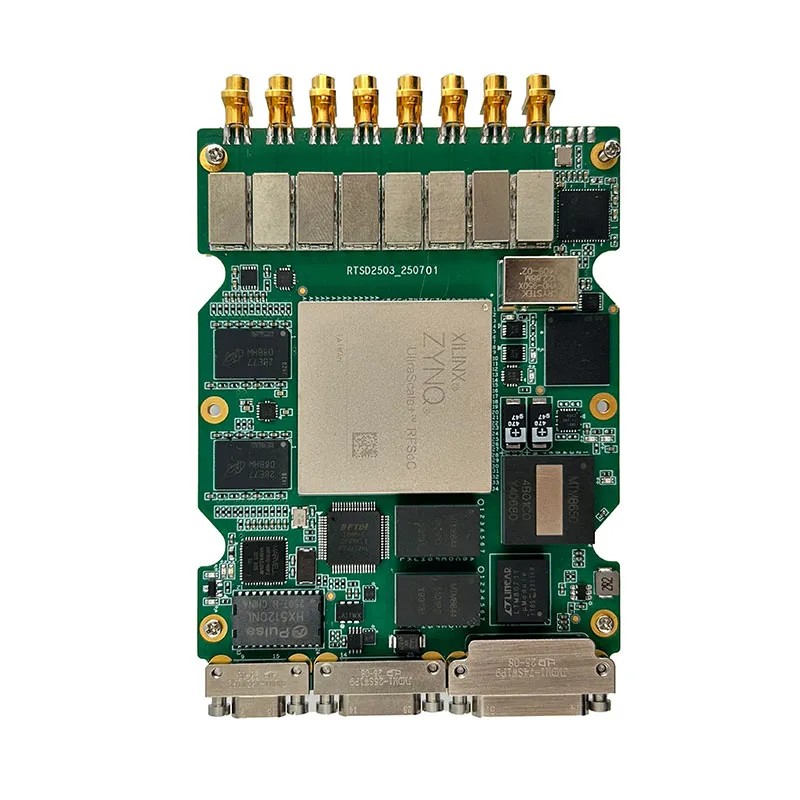

47DR_RTSD2503

47DR_RTSD2503 -

Программно-определяемое радио 4xAD9361

Программно-определяемое радио 4xAD9361 -

4T32R голографическая статическая РЛС

4T32R голографическая статическая РЛС -

SYNC_V2

SYNC_V2 -

Плата защиты напряжения

Плата защиты напряжения -

Высокоточная система синхронизации импульсов (YM_SYNC)

Высокоточная система синхронизации импульсов (YM_SYNC) -

Подключение к TV-оборудованию

Подключение к TV-оборудованию -

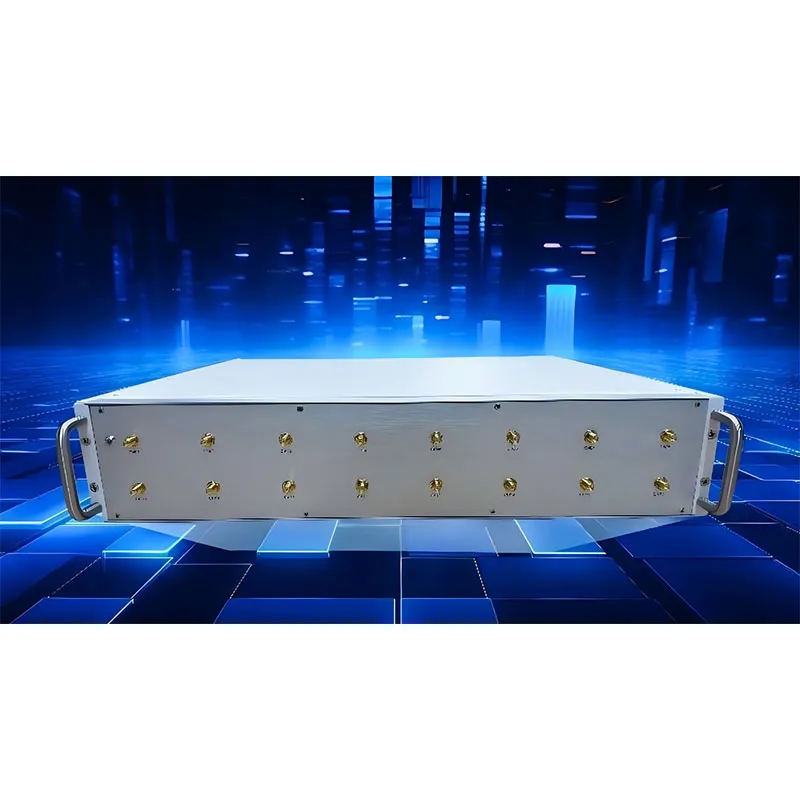

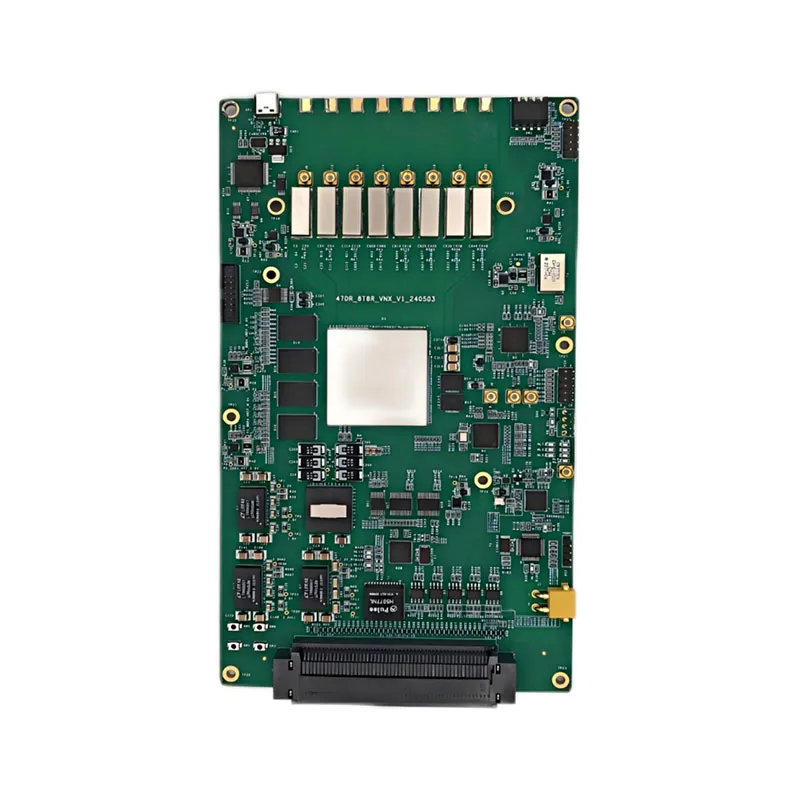

47DR_8T8R_VNX_V1

47DR_8T8R_VNX_V1 -

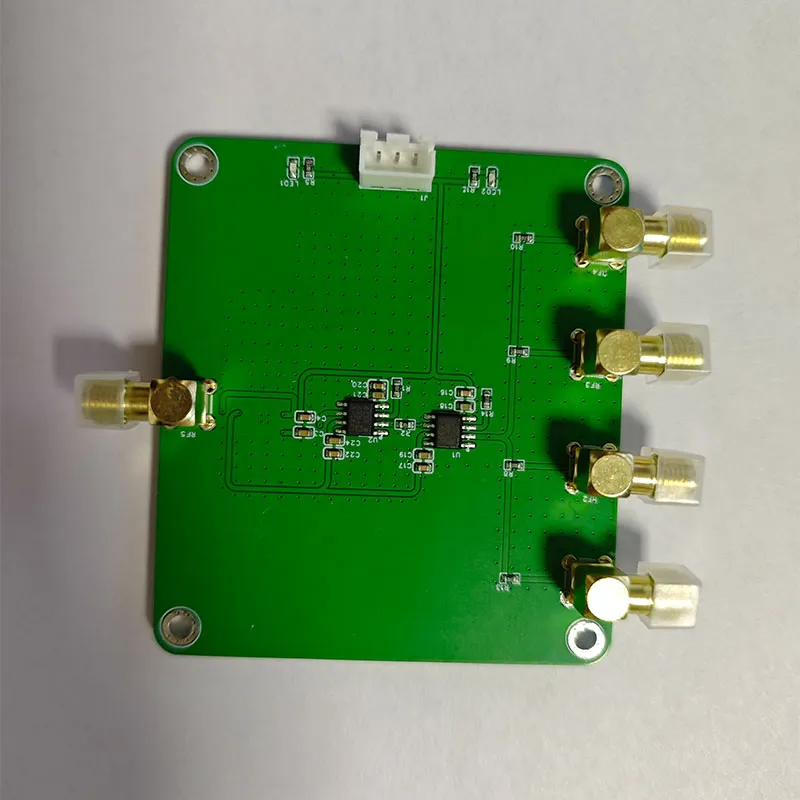

Суммирующий усилитель

Суммирующий усилитель