Печатная плата таймера

Когда слышишь ?печатная плата таймера?, многие представляют себе просто плату с микросхемой-таймером вроде NE555. Но на практике, особенно в промышленных контроллерах или системах с жесткими условиями, всё куда капризнее. Частая ошибка — недооценивать влияние паразитных параметров разводки на временные интервалы. Я сам лет пять назад попался на этом, делая плату для термостата: таймер на MCU выдавал расхождения до 10%, хотя кварц был подобран точно. Пришлось копать глубже.

От концепции к макету: где таится дьявол

Начнем с базиса. Ключевая задача печатной платы таймера — обеспечить стабильность временной базы. Это упирается не только в выбор резонатора или RC-цепи, но и в их расположение на плате. Например, трассировка тактовых линий вблизи силовых шин — верный путь к помехам. Один раз пришлось переделывать макет для заказчика из медицинской отрасли: наводки от драйвера шагового двигателя сбивали счетчик, что совершенно недопустимо.

Здесь стоит отметить подход некоторых производителей, которые глубоко интегрируют разработку и производство. Взять, к примеру, ООО Сиань Циюнь Чжисюнь Электронные Технологии. На их ресурсе apexpcb-cn.ru можно увидеть, что акцент делается не просто на изготовлении ПП, а на полном цикле — от проектирования схемы с учетом электромагнитной совместимости до тестирования готовых модулей. Это как раз тот случай, когда понимание физики процесса критично для итоговой стабильности таймера.

Что я вынес для себя? Всегда резервирую место на плате для дополнительного фильтрующего конденсатора вблизи ног таймера, даже если в симуляции всё идеально. Реальная сборка, особенно при пайке волной, может внести свои коррективы.

Материалы и слоистость: тонкости, которые влияют на точность

Выбор материала подложки — это не про маркетинг, а про диэлектрические потери и ТКС. Для высокоточных таймеров, работающих в широком температурном диапазоне, FR-4 может оказаться недостаточно. Применение специализированных материалов, например, с низким коэффициентом расширения, помогает снизить дрейф параметров. Упомянутая компания в своем развитии с 2018 года явно прошла через подобные итерации, раз выросла в группу с полным контролем цепочки — это позволяет жестко задавать стандарты на материалы.

Многослойность — еще один инструмент. Выделенный внутренний слой ?земли? под областью таймера служит экраном. Но тут есть нюанс: слепые и скрытые переходы (vias) могут добавить паразитной индуктивности. В одном проекте с таймером на несколько каналов именно это стало причиной разброса задержек между каналами. Пришлось оптимизировать топологию переходных отверстий.

Поэтому сейчас, глядя на готовые решения от интеграторов, я всегда в первую очередь изучаю сборочный чертеж и спецификацию материалов, а не только принципиальную схему.

Термодизайн и долговечность: что не увидишь в Proteus

Таймер, особенно силовой, греется. А нагрев меняет и сопротивление дорожек, и характеристики пассивных компонентов. Плата — это еще и радиатор. Недостаточная площадь медной поливки вокруг корпуса микросхемы или непродуманные термопрокиды между слоями ведут к перегреву и ускоренному старению. Я видел платы, где через год-два работы точность таймера падала на треть именно из-за деградации электролитов в RC-цепях, стоявших рядом с горячим стабилизатором.

Здесь комплексный подход к управлению всей промышленной цепочкой, как у ООО Сиань Циюнь Чжисюнь Электронные Технологии, дает преимущество. Они могут на этапе прототипирования заложить термоанализ и испытать плату в камере, а не гадать по формулам. На их сайте видно, что акцент на инновации и интеграцию — это не пустые слова, а проработка таких вот ?неочевидных? этапов, которые и определяют надежность конечного изделия.

Из личного опыта: теперь для любого таймера с током потребления выше 50 мА я сразу делаю тепловую симуляцию в привязке к конкретному корпусу и окружению на плате. Это экономит массу времени на доводке.

Вопросы тестирования и отладки на готовой плате

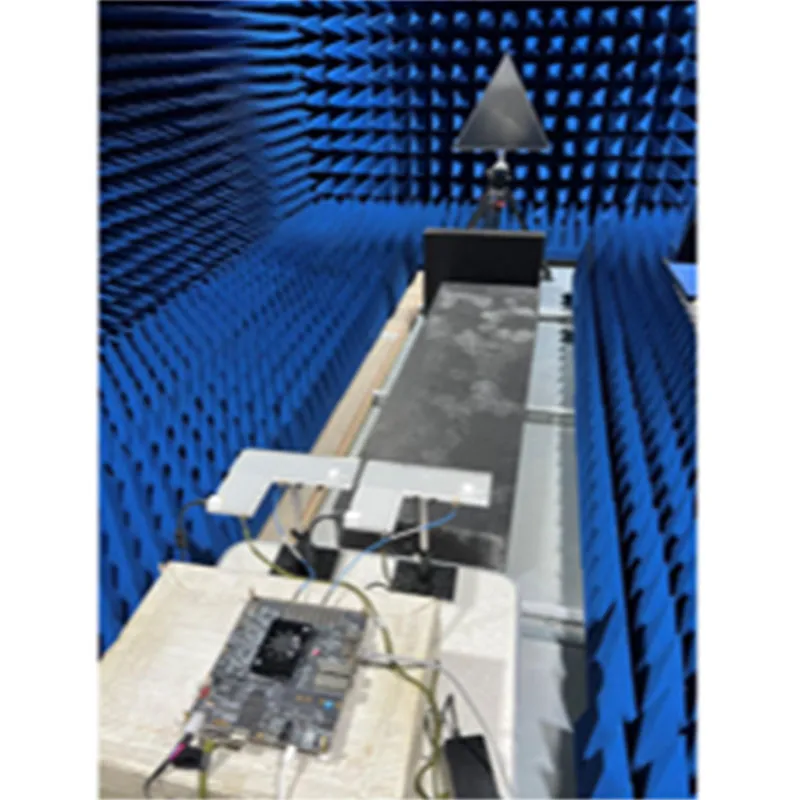

Собрали плату — и тут начинается самое интересное. Осциллограф, логический анализатор и, что важно, источник помех. Как проверить, что печатная плата таймера устойчива? Я создаю намеренно ?грязные? условия: включаю рядом импульсный блок питания, коммутирую реле. Часто проблема проявляется не в постоянном сдвиге, а в дрожании (jitter) фронтов, что губительно для синхронных систем.

Однажды столкнулся с ситуацией, когда таймер сбоил только при определенной влажности в цеху. Оказалось, гигроскопичность флюса, не смытого между ножками микросхемы, создавала утечки. После этого всегда настаиваю на полноценной отмывке плат под контролем, особенно для заказных изделий. Производители с полным циклом, как правило, имеют отработанные процессы пост-обработки, что снижает такие риски.

Отладка — это еще и умение читать осциллограммы. Нарастающий фронт на выходе таймера с заваленным углом — прямой сигнал о проблемах с разводкой или нагрузочной способностью. Иногда спасает добавление буферного элемента, но правильнее — изначально заложить правильную топологию.

Взгляд в будущее: интеграция и кастомизация

Сейчас тренд — не просто сделать плату, а интегрировать в нее таймер как часть более сложной функции: скажем, комбинация таймера, драйвера и цепи защиты. Это требует плотного взаимодействия между разработчиком схемы и технологиом производства. Способность компании контролировать несколько предприятий по цепочке, создавая синергию, как описано в профиле ООО Сиань Циюнь Чжисюнь Электронные Технологии, здесь становится ключевым конкурентным преимуществом. Можно быстро прототипировать, тестировать и вносить изменения.

Кастомизация — еще один момент. Иногда нужен не стандартный таймер, а схема с нелинейной зависимостью или коррекцией от внешнего датчика. Гибкость производства позволяет реализовать такие вещи на уровне печатной платы, внося изменения в металлизацию и набор компонентов без полной переработки проекта.

Если резюмировать, то создание надежной печатной платы таймера — это всегда баланс между теоретическим расчетом, знанием технологических ограничений и, грубо говоря, чутьем, наработанным на косяках. Это не та работа, где можно слепо положиться на автогенератор разводки. Нужно понимать, как поведет себя каждый миллиметр меди в реальных условиях, а для этого нужен именно тот опыт, который складывается из множества спроектированных и, что важно, успешно работающих в поле плат.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

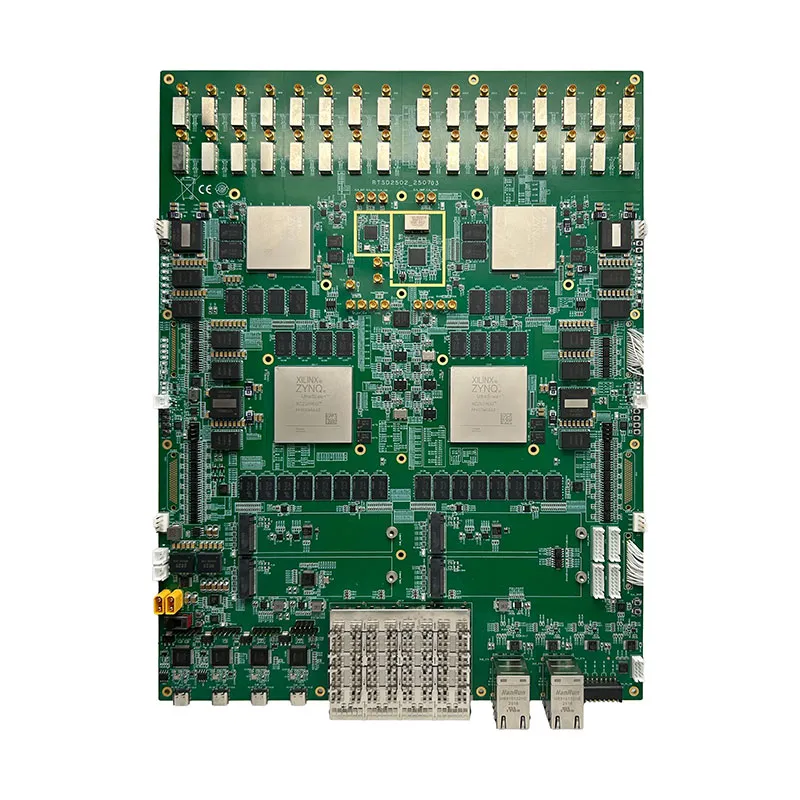

RTSD2502_250703

RTSD2502_250703 -

Подключение к TV-оборудованию

Подключение к TV-оборудованию -

Панорамная разведывательная система

Панорамная разведывательная система -

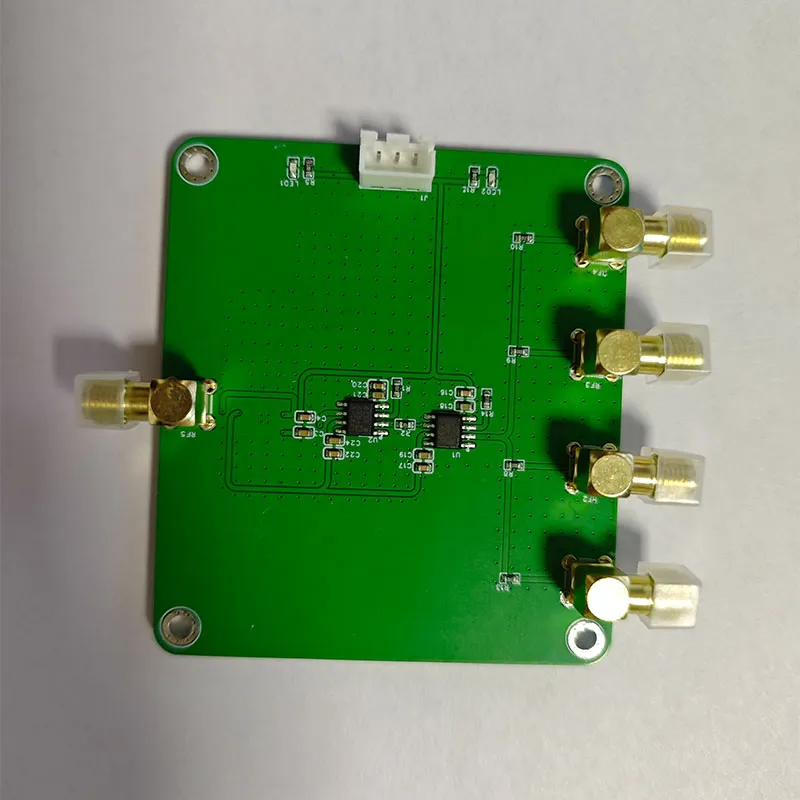

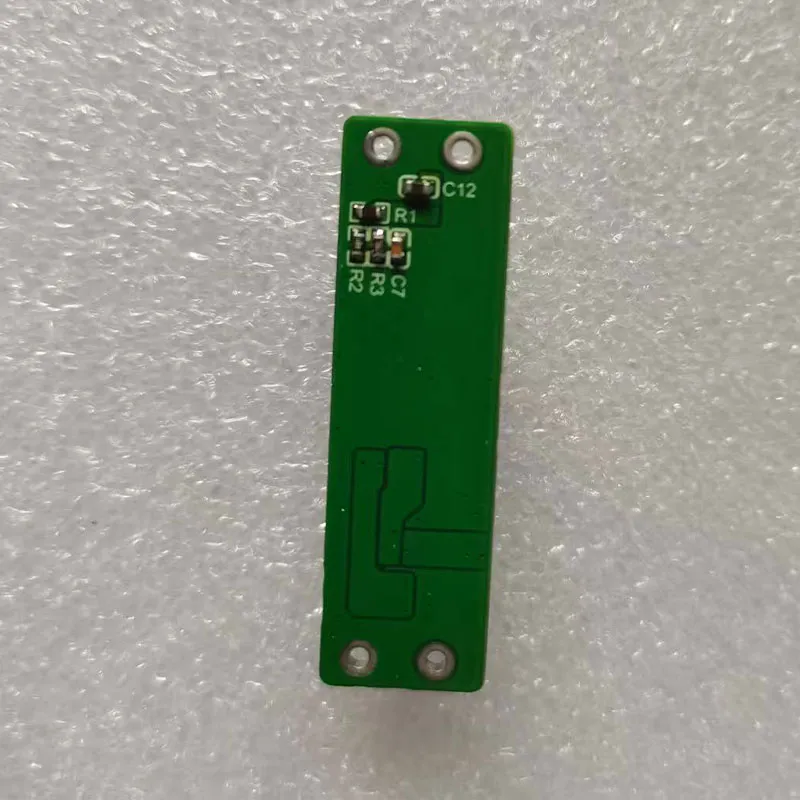

Плата защиты напряжения

Плата защиты напряжения -

47DR_SC_BJY_ZHCL_240801

47DR_SC_BJY_ZHCL_240801 -

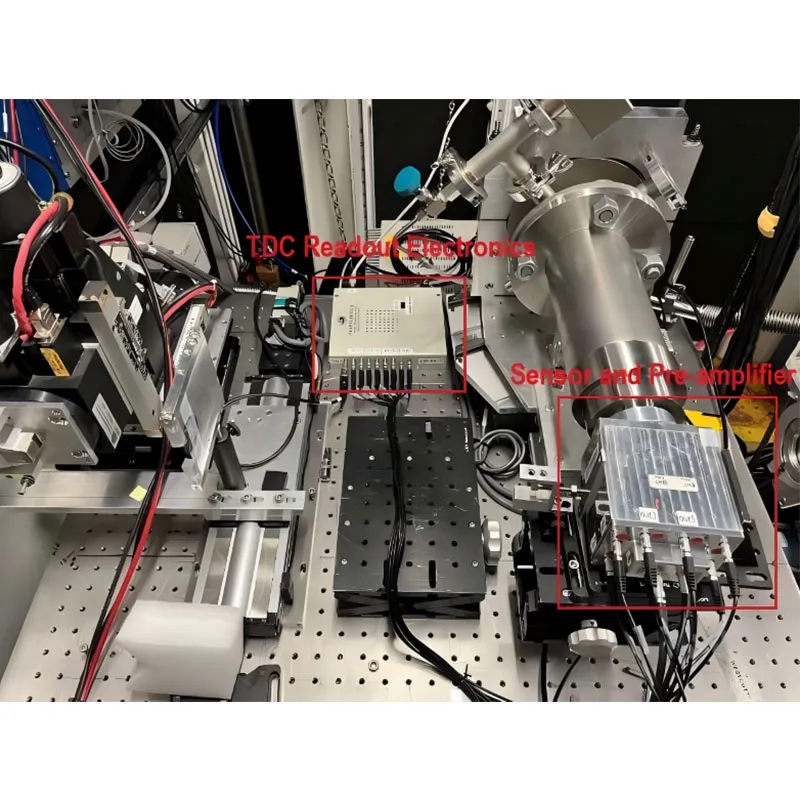

Система измерения времени (YM_TDC)

Система измерения времени (YM_TDC) -

Высокоскоростной сбор и хранение данных: Прямая запись FPGA в NVMe SSD (двухдисковый отсек)

Высокоскоростной сбор и хранение данных: Прямая запись FPGA в NVMe SSD (двухдисковый отсек) -

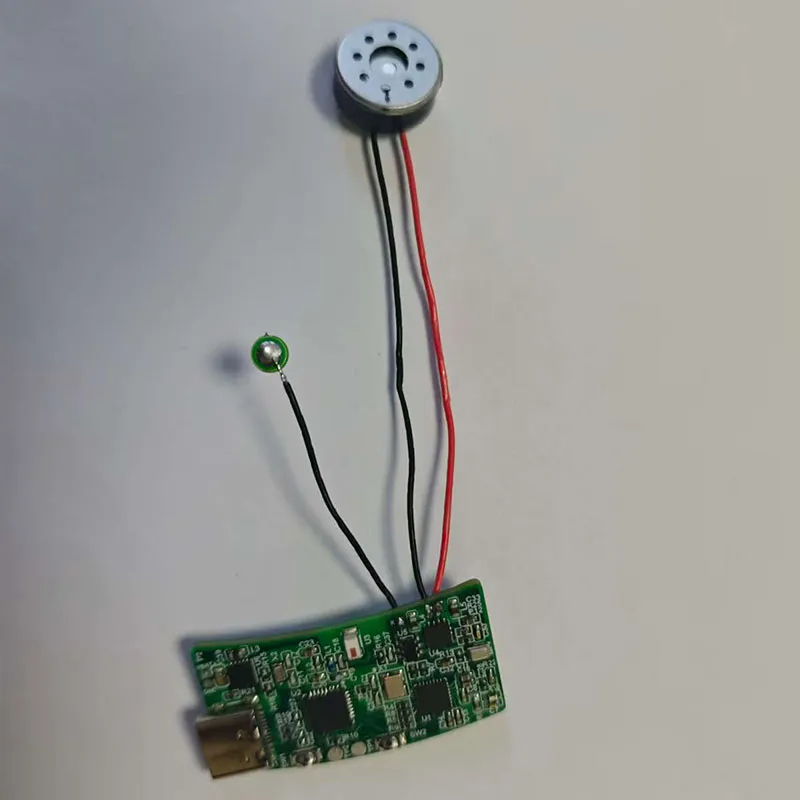

Костнопроводные наушники

Костнопроводные наушники -

64-канальное программно-определяемое радио NLY-VNX-64DBF

64-канальное программно-определяемое радио NLY-VNX-64DBF -

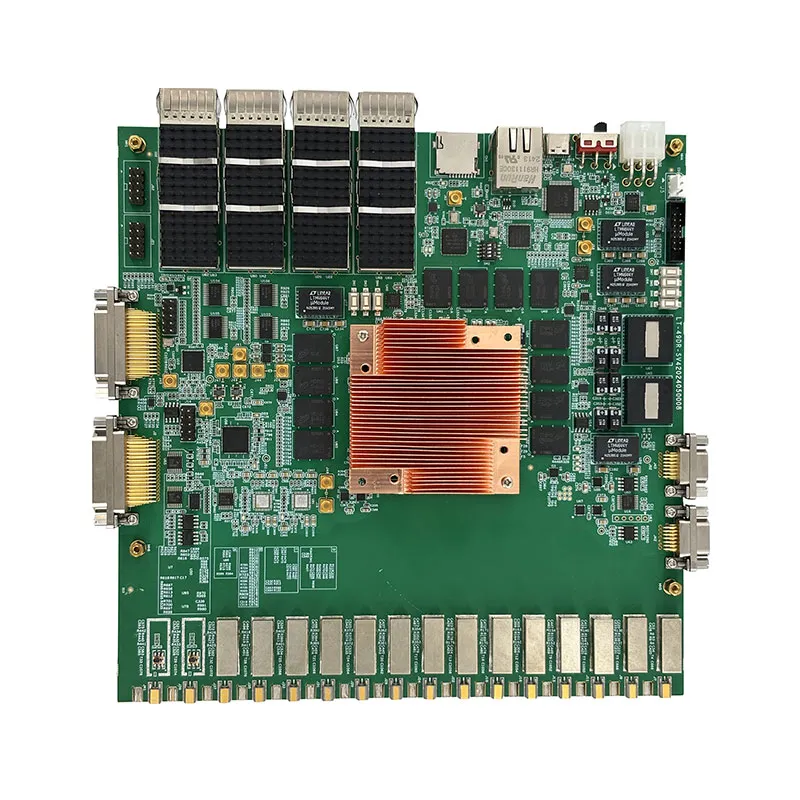

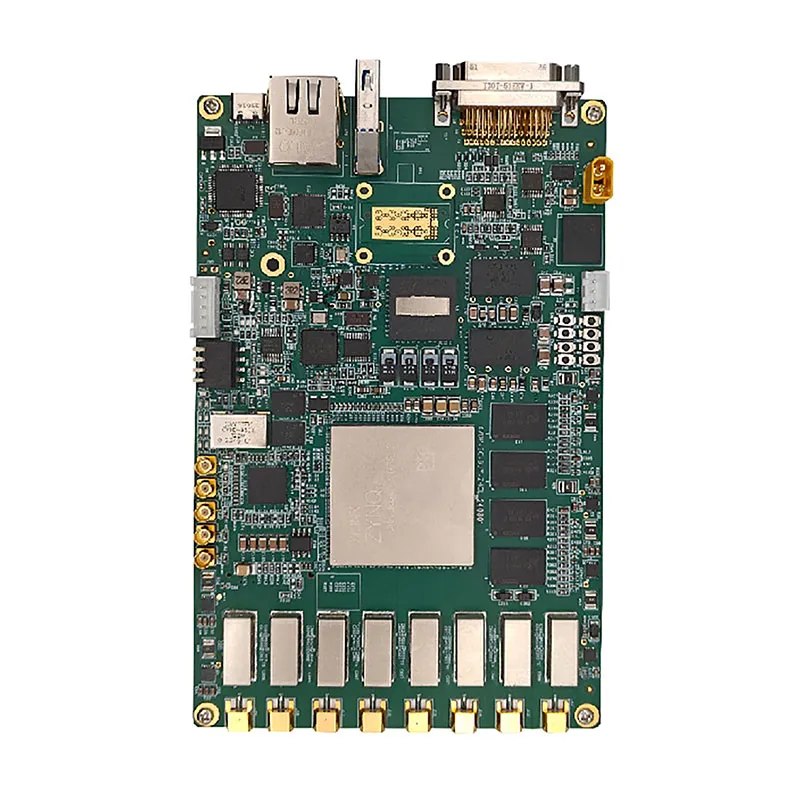

Вычислительная мощность платы FPGA+TX2i GPU составляет 40 TOPS

Вычислительная мощность платы FPGA+TX2i GPU составляет 40 TOPS -

Высокоскоростной регистратор данных

Высокоскоростной регистратор данных -

Разработка программного обеспечения

Разработка программного обеспечения