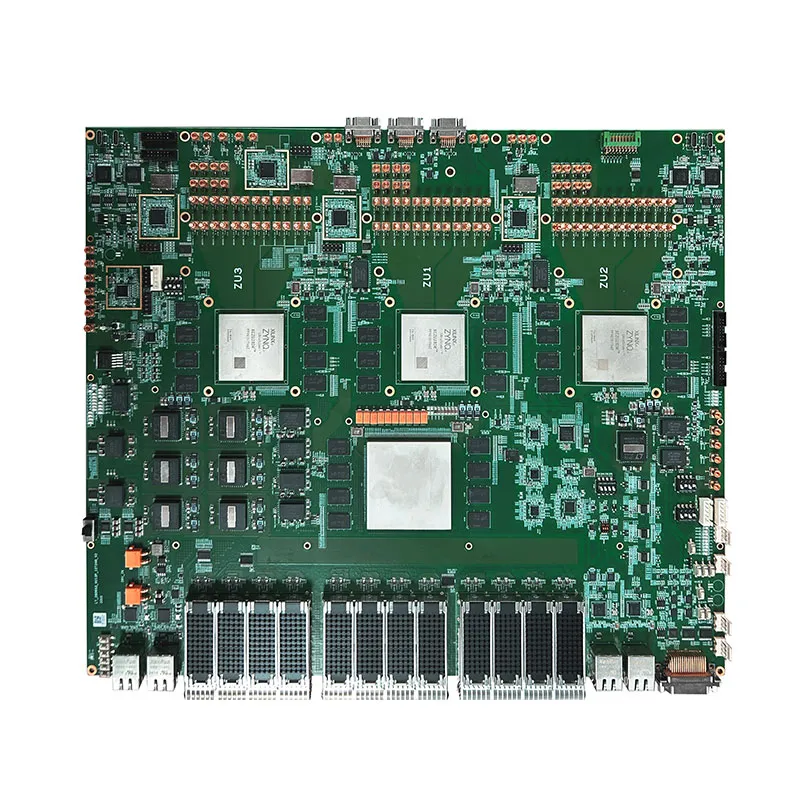

Печатная плата на чипах

Когда говорят печатная плата на чипах, многие сразу представляют что-то вроде SiP или корпусированный модуль. Но на практике, особенно в силовых или ВЧ-приложениях, это часто оказывается нечто более приземлённое и сложное одновременно — монтаж кристалла прямо на подложку, где сама подложка становится частью системы теплоотвода и электромеханической конструкции. Путаница возникает из-за того, что грань между ?платой? и ?корпусом? здесь сильно размыта.

Не просто подложка, а интерфейс

Основная сложность в работе с печатная плата на чипах — это не столько трассировка, сколько управление импедансом и тепловыми потоками на границе кристалл-подложка. Я помню один проект с силовым IGBT-модулем. Мы взяли стандартную керамическую подложку (AlN), но столкнулись с тем, что тепловое расширение медной металлизации всё равно создавало механические напряжения на контактах чипа после пайки твёрдым припоем. Пришлось переходить на послойное нанесение металлизации с буферными слоями — не самый дешёвый путь.

Именно здесь многие недооценивают роль материалов. Керамика (Al2O3, AlN, BeO) — это классика, но в последние годы для некоторых задач средней мощности стали активно рассматривать металлические основания с изолирующим слоем (IMS), особенно когда нужна большая площадь для рассеивания и относительно низкая стоимость. Но тут своя головная боль: диэлектрический слой должен выдерживать не только напряжение, но и многократные термоциклы без образования микротрещин.

В контексте сборки, сам процесс монтажа кристалла (die attach) — это целое искусство. Эпоксидные адгезивы, пайка мягким или твёрдым припоем, даже спекание наносеребряной пастой — каждый метод тянет за собой цепочку технологических ограничений по температуре, давлению, атмосфере в печи. Ошибка в выборе часто вскрывается только на этапе термоциклирования, когда отваливаются чипы или резко растёт тепловое сопротивление.

Трассировка: когда каждые 0.1 мм имеют значение

Особенность проектирования печатной платы под непосредственный монтаж чипов — в необходимости совместить ?микронные? требования разводки сигналов от контактных площадок кристалла с ?миллиметровыми? требованиями силовых цепей и внешних подключений. Часто используется гибридный подход: тонкие линии (может, даже по технологии thin-film) для сигналов управления и датчиков, и толстые, залитые медью, области для силовых шин.

Один из болезненных уроков — это влияние паразитной индуктивности в силовых контурах. В одном из ранних проектов мы красиво развели шины постоянного тока на разных слоях керамической подложки, но забыли про взаимную индуктивность. В результате, при коммутациях на высоких частотах возникали выбросы напряжения, которые буквально ?убивали? драйверы. Пришлось полностью пересматривать топологию, сводя силовую петлю к минимуму, фактически делая её ?плоской? в одной плоскости.

Ещё один нюанс — это изоляция. В силовых модулях часто требуется гальваническая развязка между цепями управления (низковольтными, подключёнными к чипу) и силовыми выводами. На керамической подложке это решается созданием изолированных областей, но их размеры и зазоры должны строго соответствовать крепопирующему напряжению. Проверка этого расчёта — обязательный пункт, который иногда упускают в погоне за компактностью.

Контроль качества и тестирование: найти невидимый дефект

Как проверить надёжность соединения кристалла с подложкой до того, как модуль будет залит компаундом или закрыт крышкой? Визуальный контроль под микроскопом — это только начало. Мы активно используем акустическую микроскопию (SAM) для выявления расслоений или пустот под чипом, особенно после пайки твёрдым припоем. Но даже SAM не всегда покажет микротрещину в припое, которая проявит себя только после 500 часов работы под нагрузкой.

Электрическое тестирование на уровне пластины (wafer probing) — это идеал, но для силовых чипов с большими контактными площадками и требованиями по току оно часто неприменимо. Поэтому многое строится на выборочном контроле и деструктивном анализе партий. Например, компания ООО Сиань Циюнь Чжисюнь Электронные Технологии в своей практике, как я слышал от коллег, делает акцент на строгом входном контроле керамических подложек и использует рентгеновский контроль для проверки качества паяных соединений после монтажа, что для ответственных применений критически важно.

Термоциклирование — это главный экзамен. Мы гоняем образцы от -40°C до +125°C, иногда с активной нагрузкой, и мониторим параметры в реальном времени. Именно здесь часто ?всплывает? несовершенство выбранного материала или технологии. Например, отказ по причине усталости металлизации на краях контактных площадок.

Практический кейс: интеграция датчиков

Современный тренд — это не просто разместить силовой чип на плате, а интегрировать в ту же подложку датчики температуры или тока. Мы пробовали впаивать миниатюрные терморезисторы (чип-резисторы) прямо рядом с кристаллом IGBT. Задача — получить быстрый отклик на перегрев кристалла. Но возникла проблема: точка пайки самого датчика становилась дополнительным тепловым сопротивлением, и показания запаздывали.

Более элегантное, но сложное решение — использовать для мониторинга температуры сам силовой чип, точнее, его p-n переход. Но это требует выделения отдельного вывода и точной калибровки, что не всегда предусмотрено производителем кристалла. Иногда приходится идти на договорённости с поставщиком чипов на уровне инженерных образцов.

Что сработало в одном из последних проектов? Мы применили тонкоплёночные платиновые датчики температуры (RTD), нанесённые методом напыления непосредственно на керамическую подложку в зоне под кристаллом. Это дало отличную тепловую связь и быстрый отклик. Но технология дорогая и требует доступа к специализированному производству. Не каждый, даже солидный интегратор, как группа компаний, контролируемая ООО Сиань Циюнь Чжисюнь Электронные Технологии, готов сразу вкладываться в такую тонкую настройку процесса для малосерийной продукции.

Взгляд в будущее и синергия в цепочке

Куда движется технология? Видится явный запрос на большую интеграцию. Не просто чип на подложке, а целая гетерогенная система: силовой кристалл, драйвер, датчики, пассивные компоненты — всё в одной компактной сборке с минимизированными паразитными параметрами. Это требует теснейшей кооперации между разработчиком чипов, производителем подложек и сборщиком модулей.

Здесь как раз проявляется сила вертикально интегрированных структур. Способность контролировать или плотно взаимодействовать с разными звеньями цепочки — от производства специализированных подложек до финального тестирования модулей — даёт огромное конкурентное преимущество. Экосистема, которую выстраивают подобные холдинги, позволяет быстрее и с меньшими рисками воплощать такие комплексные решения, как продвинутые печатная плата на чипах для электромобилей или промышленных приводов.

Однако, риски остаются. Слишком быстрое усложнение может привести к катастрофическому росту стоимости и снижению выхода годных. Баланс между производительностью, надёжностью и ценой — это по-прежнему главная инженерная задача. Иногда самое простое решение — разместить чип на стандартной изолированной медной подложке с качественной пайкой — оказывается самым живучим и востребованным на рынке. Технология должна решать проблему, а не становиться самоцелью. Это, пожалуй, главный вывод после многих лет работы с этой темой.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

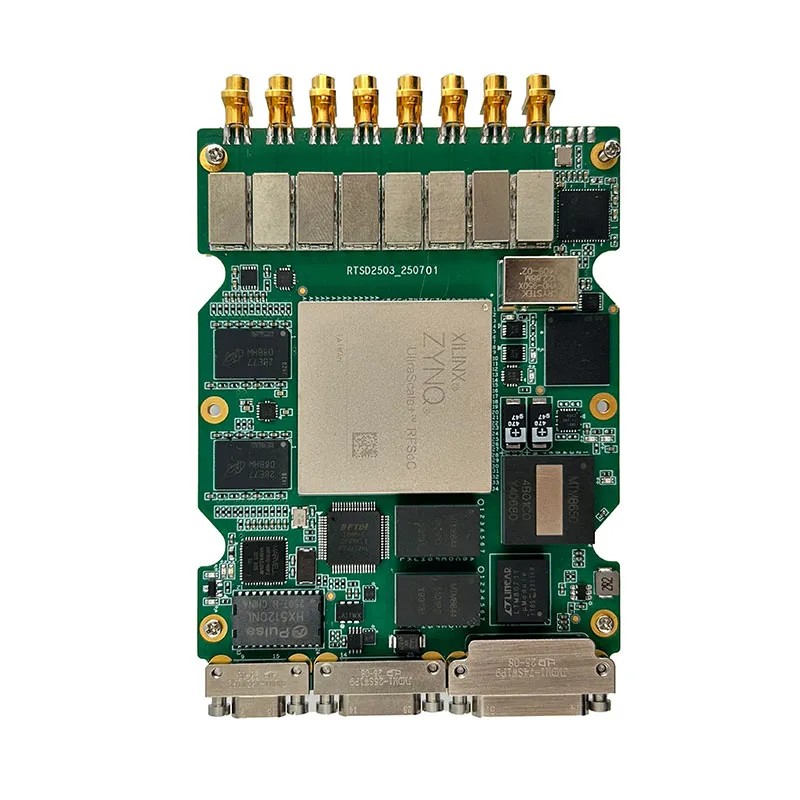

47DR_RTSD2503

47DR_RTSD2503 -

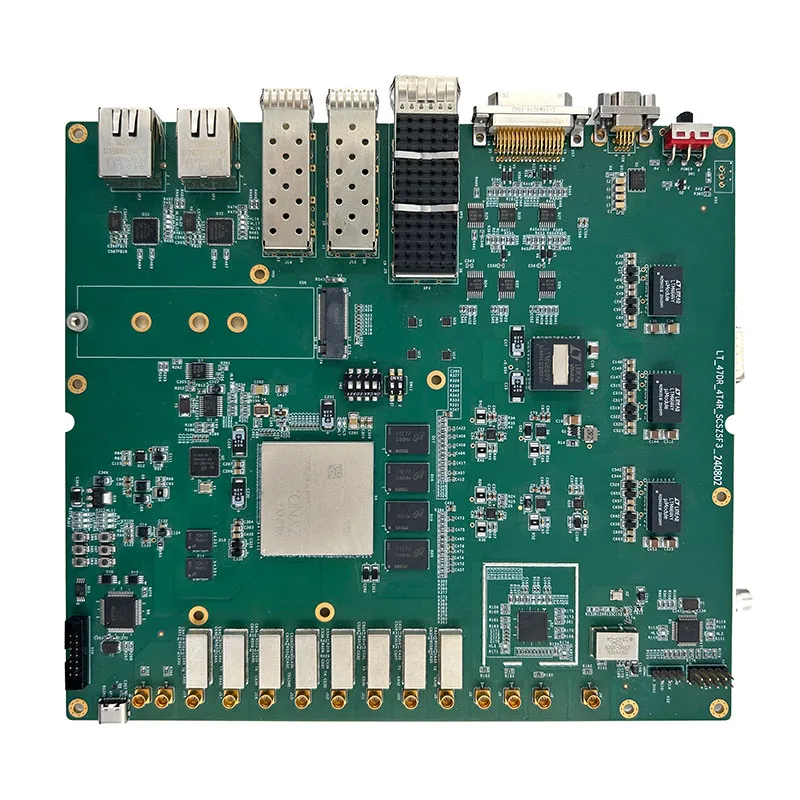

47DR_4T4R_SCSZSF3

47DR_4T4R_SCSZSF3 -

От печатной платы до готового продукта: комплексные решения для производства электроники

От печатной платы до готового продукта: комплексные решения для производства электроники -

RFSOC+8T8R+47DR+DSP6678

RFSOC+8T8R+47DR+DSP6678 -

Высокоскоростной регистратор данных

Высокоскоростной регистратор данных -

Интегрированная система связи и мониторинга БПЛА в 26 ГГц миллиметровом диапазоне

Интегрированная система связи и мониторинга БПЛА в 26 ГГц миллиметровом диапазоне -

Высокоинтегрированный MEMS IMU WT-IMU-M11

Высокоинтегрированный MEMS IMU WT-IMU-M11 -

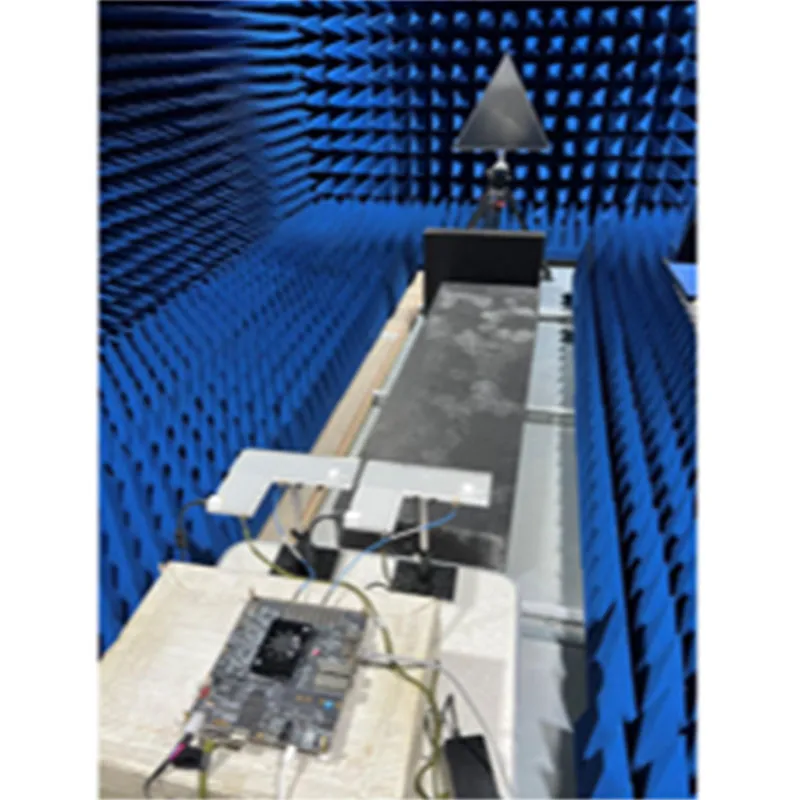

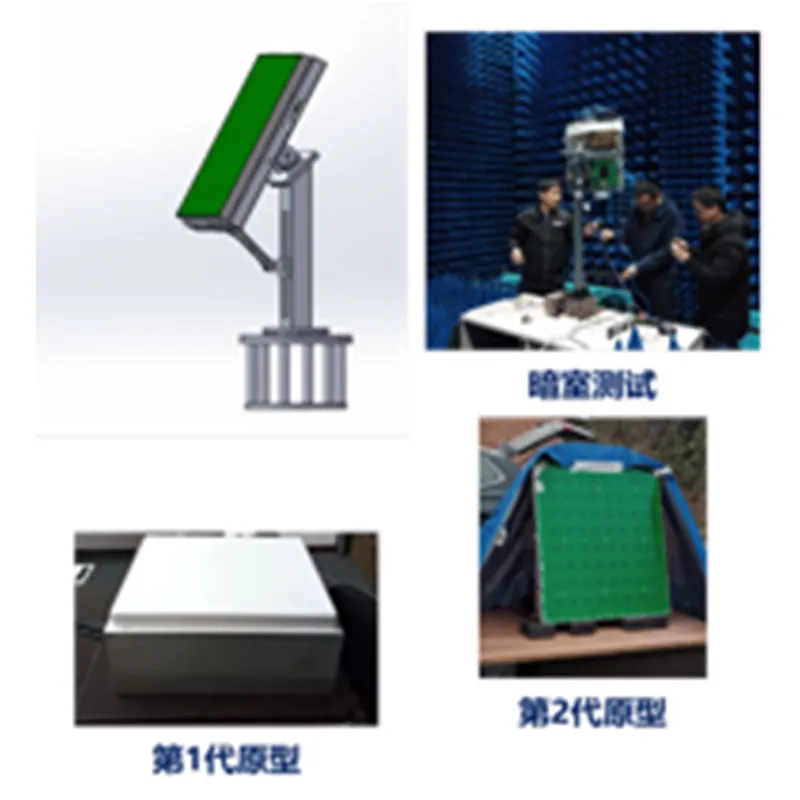

8T8R прототип программируемой РЛС

8T8R прототип программируемой РЛС -

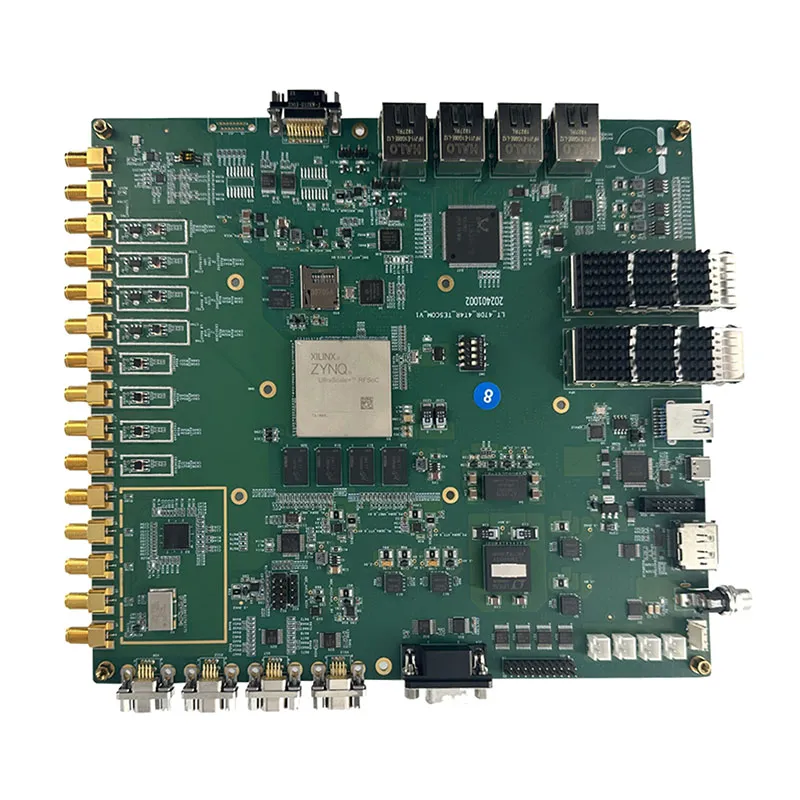

47DR_4T4R_TESCOM_V1

47DR_4T4R_TESCOM_V1 -

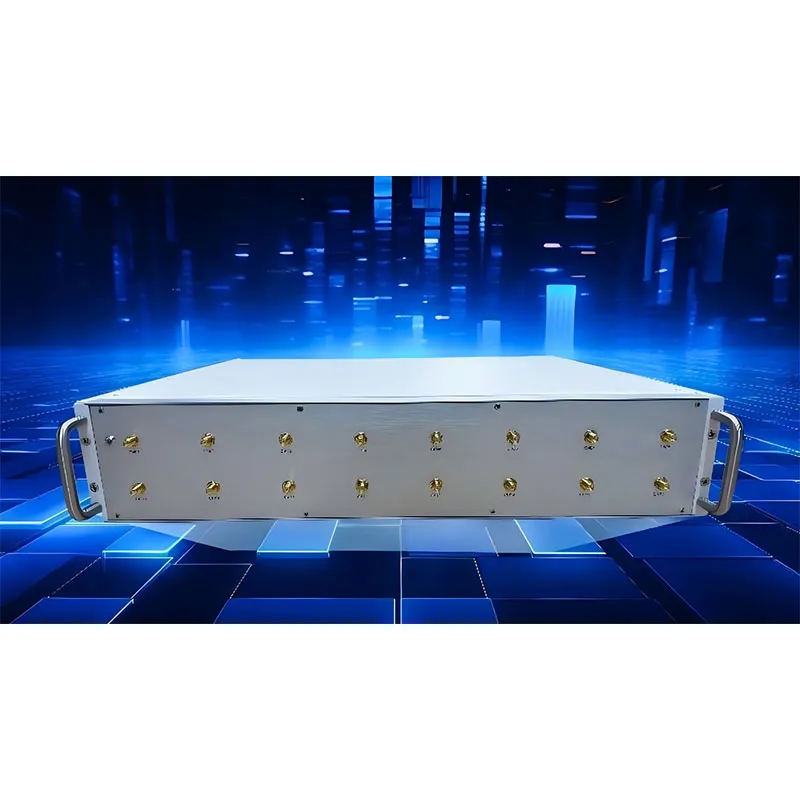

64-канальное программно-определяемое радио NLY-VNX-64DBF

64-канальное программно-определяемое радио NLY-VNX-64DBF -

Высокоточная система синхронизации импульсов (YM_SYNC)

Высокоточная система синхронизации импульсов (YM_SYNC) -

96-канальная цифровая фазированная решётка NLY-96DBF-V1.0

96-канальная цифровая фазированная решётка NLY-96DBF-V1.0