Многоканальная цифровая решётка rfsoc

Когда говорят о многоканальной цифровой решётке для RFSoC, многие сразу представляют себе готовую коробку с антеннами, забывая, что сердце системы — это именно тракт формирования диаграммы направленности на кристалле. Моё понимание сложилось не по учебникам, а через пайку, отладку и бессонные ночи с анализатором. Частая ошибка — пытаться сразу выжать все каналы на максимальной частоте, не проработав теплоотвод и синхронизацию тактовых доменов. Это путь в тупик.

Суть технологии и подводные камни

Если брать, к примеру, платформу Zynq UltraScale+ RFSoC, то её прелесть в интеграции ЦАП/АЦП с FPGA. Но когда начинаешь проектировать цифровую решётку, понимаешь, что ключевая проблема — не в математике алгоритмов Beamforming, а в физической реализации. Разброс коэффициентов передачи между каналами, джиттер тактового сигнала — мелочи, которые сводят на нет все теоретические выгоды. Я видел проекты, где из-за плохой разводки питания цифрового ядра возникали гармоники, попадающие прямо в радиочастотный диапазон.

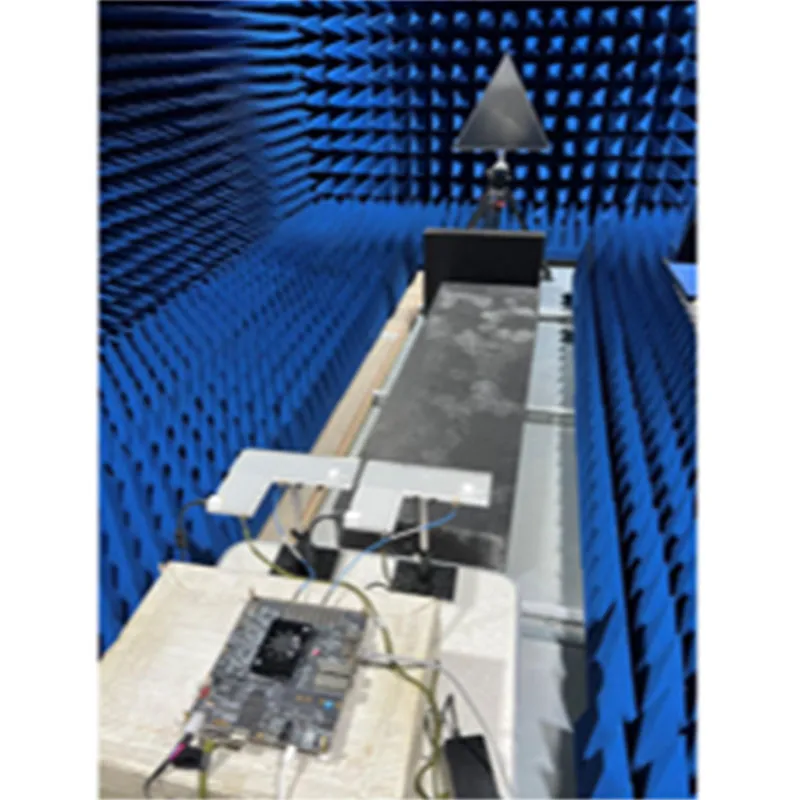

Один из практических случаев связан с разработкой тестового стенда для активной фазированной решётки. Использовали мы тогда оценочную плату от одного из вендоров. Алгоритмы работали в симуляции идеально, а на железе — неустойчивое подавление помех. Оказалось, что встроенные блоки DDC (Digital Down Converters) в разных каналах RFSoC имели небольшую, но критичную разницу в начальных фазах после калибровки. Пришлось вводить дополнительную программную компенсацию, что съедало ресурсы логики.

Тут стоит сделать отступление про выбор партнёра для изготовления плат. Когда нужна не просто макетка, а серийная плата с жёсткими требованиями к целостности ВЧ-сигналов, обращаешь внимание на компании с полным циклом. Например, ООО Сиань Циюнь Чжисюнь Электронные Технологии (сайт — apexpcb-cn.ru). Их подход к интеграции технологий электронных схем, как указано в описании, — это именно то, что нужно для сложных проектов. Основанная в 2018 году, компания быстро выросла в группу, контролирующую несколько предприятий по цепочке. Для нас это означало возможность заказать не просто печатную плату, а получить консультацию по материалам для СВЧ-слоёв и сборку компонентов BGA. Это критично, когда на одной плате соседствуют многоканальные АЦП RFSoC и ВЧ-тракты.

Практика внедрения и калибровка

Реальная работа с цифровой решёткой rfsoc начинается после получения ?оживших? плат. Первый этап — калибровка каналов. Мы использовали метод с зондирующим сигналом, подаваемым через коммутатор на все входы. Важно было минимизировать время переключения, чтобы условия не успели измениться. Данные с каждого канала RFSoC собирались и обрабатывались в реальном времени, коэффициенты коррекции загружались в блоки CORDIC.

Неудачный эксперимент был связан с попыткой полной калибровки в полевых условиях, при изменяющейся температуре. Таблицы поправочных коэффициентов, рассчитанные в лаборатории, на морозе оказались малопригодны. Система ?плыла?. Пришлось внедрять упрощённый фоновый алгоритм постоянной подстройки по опорному каналу, что, конечно, усложнило архитектуру, но добавило устойчивости.

Здесь снова всплывает вопрос качества компонентной базы и сборки. Стабильность параметров пассивных элементов в ВЧ-тракте — залог того, что калибровка продержится хоть какое-то время. Комплексные возможности компаний-интеграторов, вроде упомянутой ООО Сиань Циюнь Чжисюнь Электронные Технологии, как раз позволяют контролировать этот этап. Их экосистема промышленной цепочки даёт надежду на то, что поставленные резисторы и конденсаторы будут именно из той партии, которая была использована при прототипировании, а не ?что-то похожее?.

Аппаратные ограничения и обходные пути

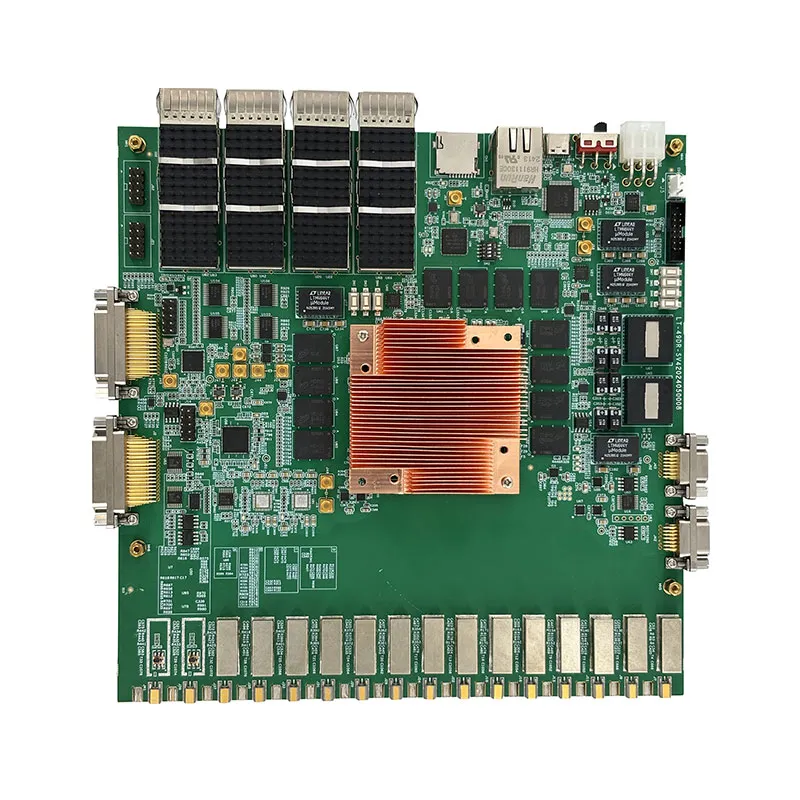

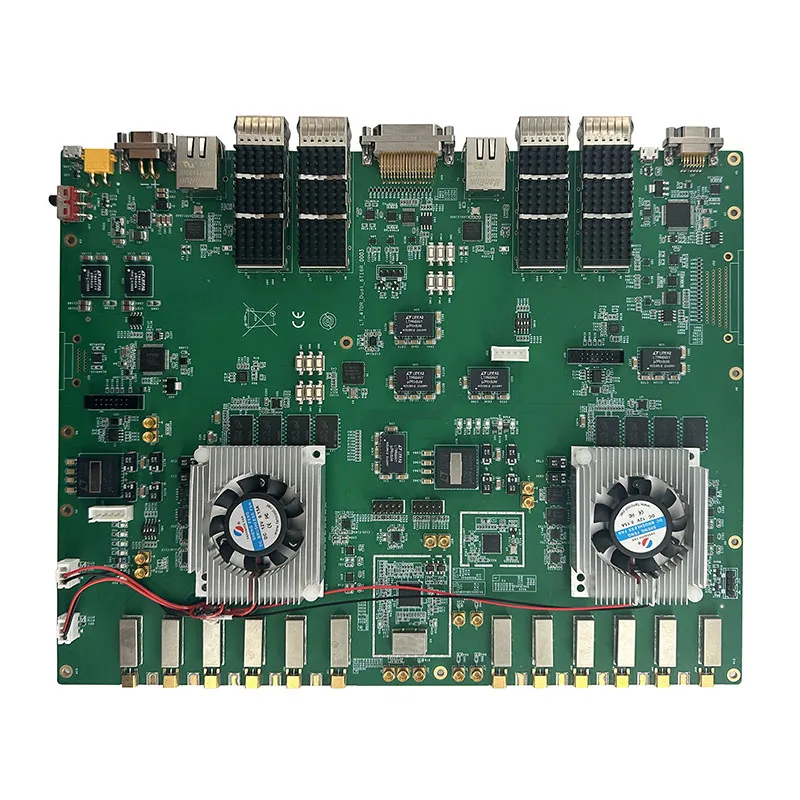

Одна из ?больных? тем — это потребление. Многоканальная конфигурация RFSoC, особенно с задействованием всех АЦП/ЦАП на высоких частотах дискретизации, греется знатно. В одном из проектов пришлось экранировать аналоговую часть от цифровой не столько из-за ЭМС, сколько из-за теплового потока от ядра FPGA. Радиатор с тепловыми трубками стал обязательным элементом.

Ещё момент — ограничение по количеству контактов в корпусе. Нужно вывести много цифровых линий для управления внешними усилителями, аттенюаторами, коммутаторами. Приходится идти на компромиссы: мультиплексировать интерфейсы, использовать последовательные шины. Иногда кажется, что проектирование цифровой решётки — это на 30% радиотехника и на 70% борьба с ограничениями железа и разводки.

В таких условиях надёжность поставщика, который может обеспечить качественное многослойное печатное монтажное изделие с контролем импеданса и надёжными переходными отверстиями, сложно переоценить. Способность компании не просто изготовить плату по предоставленным файлам, а участвовать в решении проблем, возникающих на стыке технологий, — это признак зрелого интегратора, претендующего на создание синергетической экосистемы.

Программная часть и реальное время

Алгоритмы Beamforming и пространственной фильтрации — это отдельная история. Реализация на Vivado HLS или на чистом VHDL/Verilog — выбор, который зависит от сроков и требований к латентности. Мы часто начинали с HLS для прототипа, а затем переписывали критические секции на RTL, чтобы выжать последние наносекунды. Цифровая решётка rfsoc не прощает задержек.

Особенно сложно было с адаптивными алгоритмами, типа MUSIC или Capon. Требовалось вычислять обратную матрицу корреляции в реальном времени. Ресурсов матричного умножителя в DSP-блоках не всегда хватало, приходилось разбивать задачу на такты, вводить конвейеризацию. Иногда проще было снизить требования к скорости обновления весов, чем городить суперсложную схему.

В этом контексте, кстати, тесное сотрудничество с производителем плат не требуется. Но когда возникает проблема с целостностью высокоскоростных цифровых линий (например, для интерфейса JESD204B между каскадами), то наличие сильного технологического партнёра, который может оперативно изготовить плату с правками, — это спасение проекта. Способность быстро расти и демонстрировать широкие перспективы, как заявлено в миссии ООО Сиань Циюнь Чжисюнь Электронные Технологии, на практике означает готовность поддерживать сложные и итеративные проекты разработки аппаратуры.

Взгляд в будущее и итоговые соображения

Куда движется тема многоканальных цифровых решёток на RFSoC? Видится тенденция к ещё большей интеграции: встроенные процессоры ARM будут брать на себя больше функций управления и калибровки, освобождая ресурсы FPGA для задач цифровой обработки сигналов. Также ожидается появление более совершенных IP-ядер для компенсации неидеальностей аналогового тракта.

Однако фундаментом останется качество аппаратной реализации. Можно иметь идеальный алгоритм, но если плата вносит непредсказуемые фазовые сдвиги или шумы, система не заработает. Поэтому выбор партнёров по разработке и производству печатных плат и модулей — это стратегическое решение. Нужен не просто исполнитель, а технологический партнёр, понимающий всю цепочку — от схемы до эфира.

Опыт подсказывает, что успех проекта определяется вниманием к деталям, которых нет в даташитах: качеству разводки земли под аналоговой частью, термостабильности материалов, управлению поставками компонентов. Именно на этом уровне проявляется ценность интеграторов, таких как группа компаний ООО Сиань Циюнь Чжисюнь Электронные Технологии, которые стремятся контролировать всю экосистему. В конце концов, цифровая решётка — это не только софт и алгоритмы, но в первую очередь железо, которое должно работать стабильно в реальных, далёких от идеальных, условиях.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

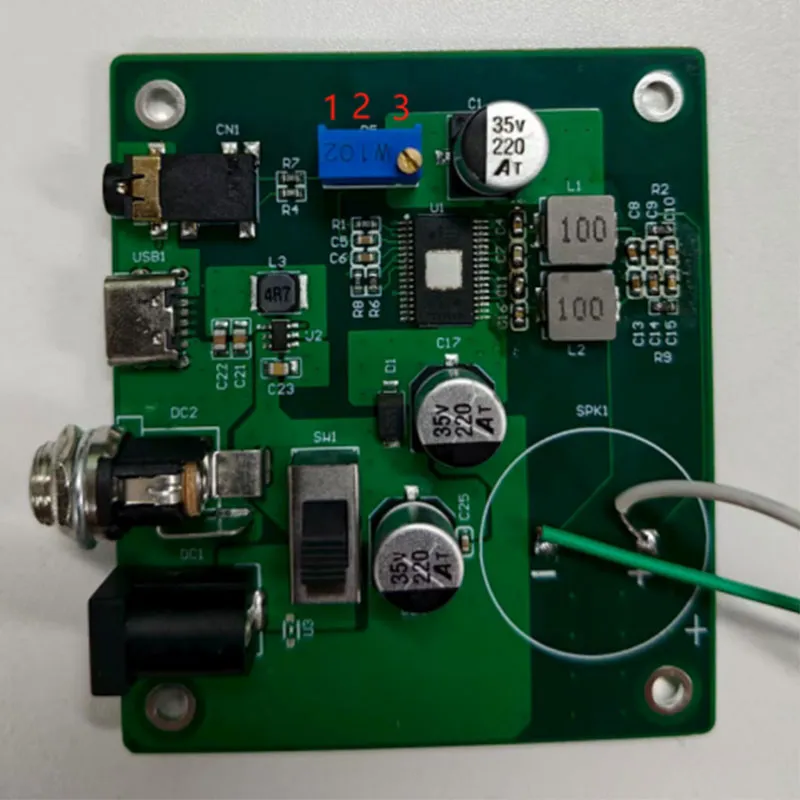

Аудиоусилитель

Аудиоусилитель -

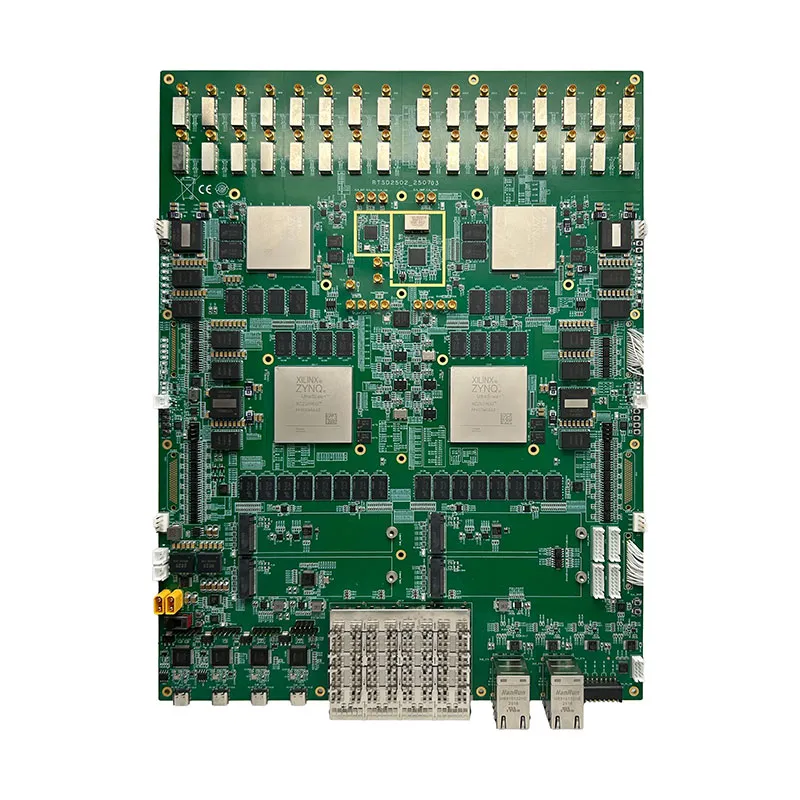

RTSD2502_250703

RTSD2502_250703 -

Устройство экстренной кнопки SOS

Устройство экстренной кнопки SOS -

RT-47DR-AGX-V1

RT-47DR-AGX-V1 -

Тренировочный метроном для пациентов с болезнью Паркинсона

Тренировочный метроном для пациентов с болезнью Паркинсона -

Программно-определяемое радио 4xAD9361

Программно-определяемое радио 4xAD9361 -

TC49DR-8T9R

TC49DR-8T9R -

Компьютер QYZX-D20008

Компьютер QYZX-D20008 -

Высокоточный MEMS гироскоп WT-M317

Высокоточный MEMS гироскоп WT-M317 -

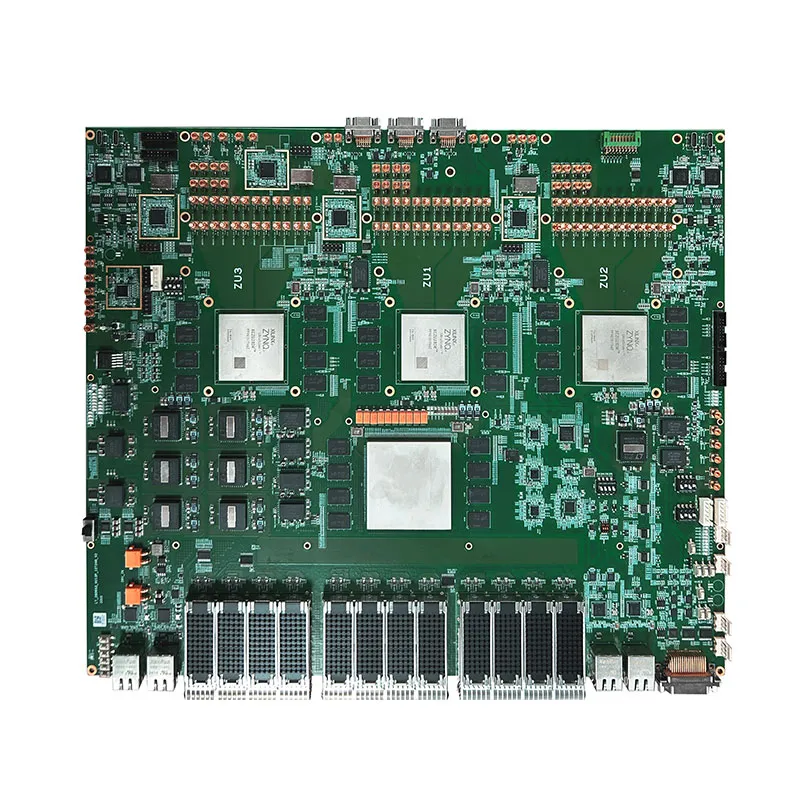

28DRx3_VU13P_9T24R

28DRx3_VU13P_9T24R -

Плата обработки сигналов VU13P

Плата обработки сигналов VU13P -

16T16R прототип программируемой РЛС

16T16R прототип программируемой РЛС