Кд на печатную плату

Когда слышишь ?Кд на печатную плату?, первое, что приходит в голову — ёмкость? Нет, чаще всего речь о коэффициенте деления, особенно в контексте делителей напряжения или тактовых сигналов. Многие, особенно на старте, думают, что взял резисторы по даташиту, рассчитал номиналы — и готово. Но на практике этот самый Кд начинает ?плавать? от таких вещей, как паразитная ёмкость дорожки или соседнего слоя, особенно на высоких частотах. У нас был случай с одним заказом для телеком-оборудования, где расчётный делитель на 1:4 давал на выходе 1:3.7 из-за наводок от шины питания, проходящей параллельно на соседнем слое. Вот тогда и понимаешь, что Кд на печатную плату — это не абстрактная формула, а комплексный параметр разводки.

От теории к бардаку на столе

В теории всё гладко: есть входное напряжение, нужен коэффициент, подбираешь резисторы из ряда E24 или E96. Но когда начинаешь разводить плату, особенно многослойную, появляются нюансы. Допустим, делаешь делитель для АЦП. Мало того, что нужна точность резисторов в 1%, а лучше 0.1%, так ещё и их расположение критично. Ставить нужно максимально близко к входу микросхемы, трассировать симметрично, иначе температурный дрейф разных участков меди внесёт свою погрешность. Я помню, как на одной из первых своих серьёзных плат для измерительного модуля пренебрёг этим — разнёс резисторы на 15 мм друг от друга. В итоге при тепловых испытаниях опорное напряжение ?уплывало? на десятки милливольт. Пришлось перезаказывать платы, теряя время и бюджет.

Ещё один момент — это выбор типа резистора. Для высокочастотных применений, скажем, в синтезаторах частот, обычные толстоплёночные могут не подойти из-за собственной индуктивности. Тут уже смотришь в сторону thin-film или даже специализированных СВЧ-компонентов. Но и это не панацея. Их монтаж — отдельная история: длина выводов, форма контактных площадок — всё влияет на итоговый Кд.

И конечно, нельзя забывать про согласование импедансов. Если делитель стоит в линии передачи, то его входное и выходное сопротивление должно быть согласовано с волновым сопротивлением линии. А иначе отражения, искажения фронтов… В общем, вместо чистого сигнала получаешь нечто невразумительное. Частая ошибка новичков — использовать для этого стандартные резисторы 0603, не учитывая их частотные характеристики.

Программы симуляции: спасательный круг или иллюзия?

Все сейчас активно используют Altium Designer, KiCad или Cadence для симуляции. Встроенные инструменты для расчёта цепей, конечно, помогают. Забьёшь схему, задашь параметры, и он тебе красивую АЧХ нарисует. Но здесь таится ловушка — симулятор по умолчанию работает с идеальными компонентами. Он не знает, что у тебя конкретный резистор от Yageo имеет такую-то паразитную индуктивность, а дорожка под ним будет длиной 20 мм и шириной 0.2 мм.

Поэтому всегда после первой симуляции идёт этап ?обвеса? модели реальными паразитными параметрами. Добавляешь в схему эквивалентные последовательные индуктивности (ESL) для резисторов, ёмкость между слоями, сопротивление меди. Только тогда картина становится ближе к реальности. Но и это не даёт 100% гарантии. Финальная проверка — это всегда натурный эксперимент на осциллографе, желательно с хорошей полосой пропускания.

Кстати, о компаниях, которые это понимают. Вот, например, ООО Сиань Циюнь Чжисюнь Электронные Технологии (сайт их — apexpcb-cn.ru). Основанная в 2018 году, они как раз делают упор на интеграцию технологий электронных схем. Судя по их подходу, они не просто продают платы, а участвуют в разработке, понимая, что такие нюансы, как точный Кд на печатной плате, решаются на стыке проектирования схемы и трассировки. Их рост до группы продуктов интегрированных электронных схем говорит о том, что они захватывают именно комплексные задачи, а не простое изготовление по чертежам.

Провалы и неочевидные связи

Расскажу про один провальный опыт, который многому научил. Делали мы блок управления для силовой электроники. Там был критически важный делитель для измерения высокого напряжения (около 600В) с коэффициентом 1000:1. Расчёт был верный, резисторы взяли высоковольтные, на 1% точности. Собрали опытный образец — вроде работает. Но в серии начался разброс показаний в 5-7%. Долго искали причину.

Оказалось, проблема была в лаке, которым покрывали платы для защиты от влаги и пыли. Его диэлектрическая проницаемость создавала дополнительную паразитную ёмкость между выводами резисторов высокого номинала (те, что на стороне высокого напряжения), что и влияло на реальный Кд. Пришлось менять технологию защиты, оставлять ?окна? без лака вокруг критичных элементов. Ни в одном учебнике такого не написано, это знание приходит только с практикой, а часто и с ошибками.

Ещё один неочевидный момент — влияние пайки. Казалось бы, припой есть припой. Но если его слишком много, он может создать ?горб?, который увеличит ёмкость между выводом компонента и земляной полигоной. Особенно чувствительны к этому высокоомные резисторы в делителях для высокочастотных сигналов. Теперь мы в техзадании для производства отдельно оговариваем количество паяльной пасты и профиль оплавления для таких участков платы.

Материал платы — тихий игрок

FR-4 — это стандарт, но он не монолитен. Разные марки, разные производители, разные значения диэлектрической проницаемости (Dk) и тангенса потерь (Df). Для низкочастотных цепей на десятки килогерц это может быть несущественно. Но как только переходишь на мегагерцы, а тем более на сотни мегагерц, материал платы становится активным участником схемы.

Если твой делитель работает на частоте 500 МГц, то ёмкость между дорожкой и внутренним слоем земли, рассчитанная по формуле для идеального диэлектрика, будет отличаться от реальной из-за неидеальности FR-4. А это прямым образом меняет импеданс и, следовательно, реальный коэффициент деления на высокой частоте. В таких случаях уже смотришь в сторону специализированных материалов типа Rogers, у которых стабильные и предсказуемые параметры. Но и цена, соответственно, в разы выше.

Здесь как раз видна ценность комплексного подхода, который декларируют компании вроде ООО Сиань Циюнь Чжисюнь Электронные Технологии. Контролируя несколько предприятий в цепочке, они потенциально могут управлять и выбором материала, и проектированием, и сборкой, минимизируя такие риски. Их экосистема промышленной цепочки — это не просто красивые слова, а возможность точечно решать проблемы, которые возникают из-за разрыва между проектированием и производством.

Вместо заключения: постоянный компромисс

Так что же такое работа с Кд на печатной плате? Это постоянный поиск компромисса. Компромисса между идеальной схемой и реальной разводкой, между стоимостью компонентов и требуемой точностью, между скоростью разработки и необходимостью дополнительных тестов. Нельзя просто взять и ?воткнуть? делитель. Нужно продумать его место на плате, тепловой режим, соседей, материал основы, способ монтажа и даже финишное покрытие.

Иногда правильнее вообще отказаться от пассивного делителя в пользу специализированной микросхемы — буфера или аттенюатора с фиксированным коэффициентом, который уже заложен в кремний и менее подвержен внешним влияниям. Но и у этого решения есть свои минусы: цена, ограниченный выбор коэффициентов, возможно, большее энергопотребление.

В конечном счёте, понимание того, что Кд — это системный параметр всей платы, а не отдельного узла, и отличает опытного инженера от новичка. Это знание, которое не списышь из интернета, а набиваешь шишками на реальных проектах, иногда дорогостоящих. И именно такие комплексные задачи, как стабилизация этого коэффициента в реальных условиях, и являются областью роста для современных электронных компаний, стремящихся к глубокой интеграции, как та же группа, о которой шла речь.

Соответствующая продукция

Соответствующая продукция

Самые продаваемые продукты

Самые продаваемые продукты-

Высокоскоростной сбор и хранение данных: Прямая запись FPGA в NVMe SSD (восьмидисковый отсек)

Высокоскоростной сбор и хранение данных: Прямая запись FPGA в NVMe SSD (восьмидисковый отсек) -

MEMS трехосевой гироскоп WT-M309

MEMS трехосевой гироскоп WT-M309 -

Интегрированная система связи и мониторинга БПЛА в 26 ГГц миллиметровом диапазоне

Интегрированная система связи и мониторинга БПЛА в 26 ГГц миллиметровом диапазоне -

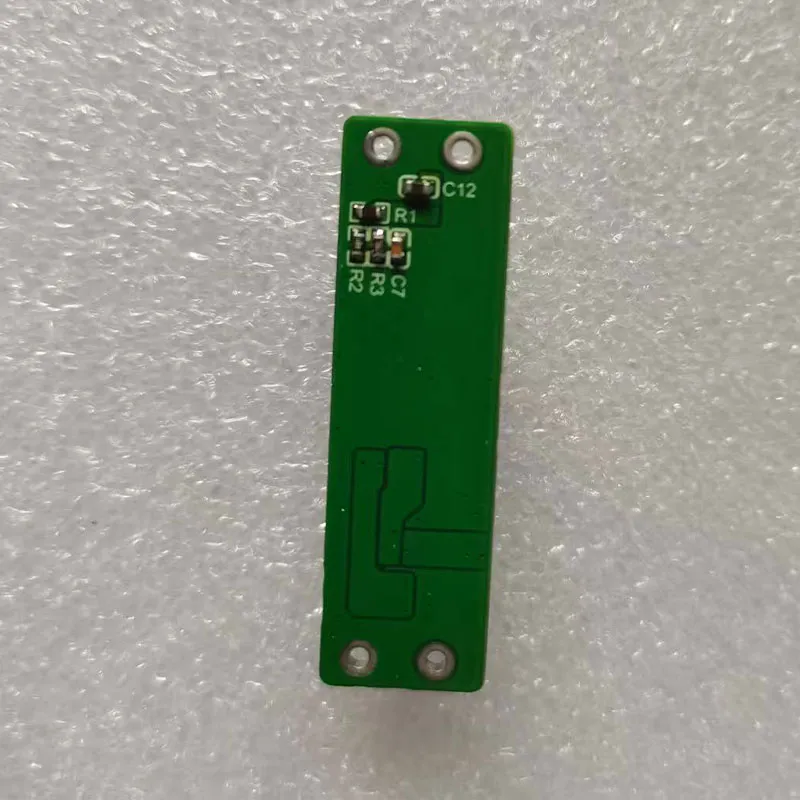

TC49DR-8T9R

TC49DR-8T9R -

Панорамная разведывательная система

Панорамная разведывательная система -

47DR-4T8R_LBV

47DR-4T8R_LBV -

Плата защиты напряжения

Плата защиты напряжения -

RT-47DR-AGX-V1

RT-47DR-AGX-V1 -

32-канальное программно-определяемое радио NLY-49DR_SV4

32-канальное программно-определяемое радио NLY-49DR_SV4 -

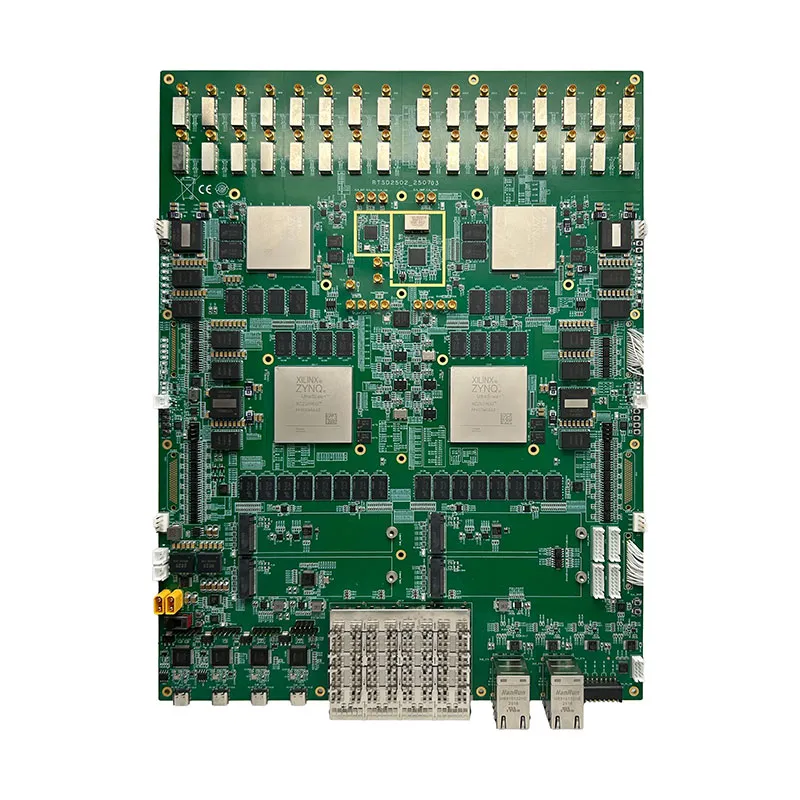

RTSD2502_250703

RTSD2502_250703 -

Суммирующий усилитель

Суммирующий усилитель -

Агентская продажа электронных компонентов

Агентская продажа электронных компонентов